Synthétiseur de fréquence : PLL, DDS

Note à l’attention des débutants : qu’est-ce qu’une PLL

Ce qui suit est un paragraphe de vulgarisation, et comme tel truffé d’imprécisions et d’erreurs par omission ou par excès de simplification.

Boucle à verrouillage de phase - PLL

Un oscillateur à boucle de phase est un « machin » destiné à générer une fréquence variable avec la stabilité d’un quartz (élément très stable en fréquence mais non variable).

Comment fonctionne une PLL ? Tout simplement en utilisant un VCO (Voltage controled oscillator), un oscillateur commandé en tension.

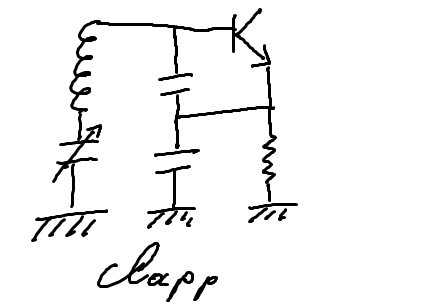

L’on sait qu’un oscillateur « simple » est constitué d’une bobine, d’un condensateur et d’un élément « actif » (généralement un transistor) destiné à générer et entretenir l’oscillation. La fréquence de l’oscillation est fonction de la valeur du condensateur et de la bobine (ou self). Si l’on fait varier la bobine, la fréquence change… idem pour le condensateur.

L'ennui, c'est que pour ajuster la fréquence, il faut "mettre la main à la pâte", ou plus exactement "tourner un bouton". Lequel fera varier un condensateur "variable", ou modifiera la valeur de la self à l'aide de noyaux faits de matériaux magnétiques. Tout çà n'est pas très pratique... il serait plus intelligent de trouver un moyen qui permette de faire varier notre circuit oscillant de manière automatique... ou plus exactement électronique.

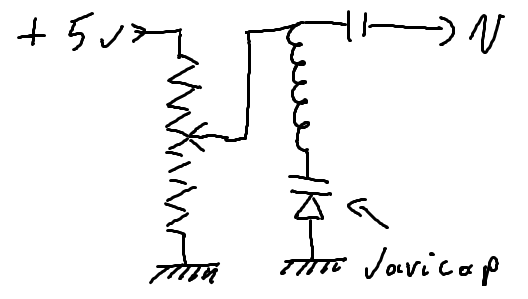

Or, il existe dans le commerce des composants –les diodes « varicap »- qui se comportent comme des condensateurs dont la valeur varie selon la tension que l’on applique sur la cathode. Un transistor, une varicap, une self, voilà notre VCO tout monté.

La tension aux bornes de la Varicap peut provenir d'un ampli op, par exemple, ou d'un microcontroleur, bref, d'un système capable de délivrer une tension variable.

Reste que ce montage n’est absolument pas stable. Les variations de température, la propreté et la stabilité de l’alimentation, les variation de saturation du noyau de la bobine font que l’on peut s’attendre à une variation de fréquence pouvant dépasser 1 Hz par seconde. Totalement inexploitable en instrumentation.

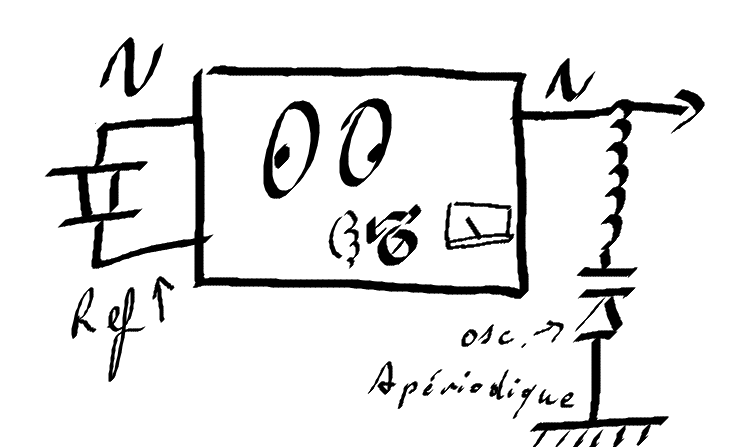

C’est là qu’intervient la fameuse « boucle à verrouillage de phase ». Il s’agit d’un circuit intégré qui joue le rôle de comparateur entre la fréquence du VCO (à droite) et une fréquence réputée stable délivrée par un quartz (à gauche ci-dessous). En d'autres termes, une PLL est un peu comme un ampli op monté en comparateur, à la différence près que ce circuit ne compare pas des tensions, mais des fréquences.

Si la fréquence est trop haute ou trop basse, le rapport cyclique entre les deux horloges va générer un troisième signal dont le rapport cyclique va varier proportionnellement à l’écart de fréquence entre F ref et F vco.

Il suffit de « redresser » ce rapport cyclique pour obtenir une tension moyenne dont la valeur va être fonction dudit rapport cyclique, donc de l’écart de fréquence à « rattraper ». L’on remarquera que tel que, la pll ne sert à rien, puisqu’elle compare par exemple un signal VCO de 4 MHz avec une horloge de référence de 4 MHz. Autant utiliser un quartz et ne pas s’enquiquiner.

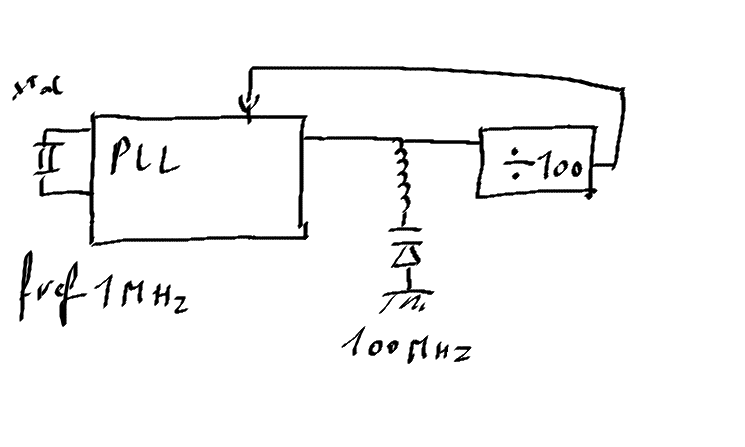

Mais avec deux sous d’astuce, l’on peut produire quasiment toutes les fréquences imaginables. Par exemple, si l’on souhaite générer un signal à 40 MHz, il suffit de construire un VCO pour cette bande, puis diviser le signal par 10… lequel pourra être alors comparé à l’horloge de 4 MHz. Car électroniquement parlant, diviser un signal est une opération très facile avec certains composants logiques. Une bascule ou un couple AND/Buffer-inverseur font d'excellent diviseurs par deux. Avec des diviseurs complexes, il est ainsi possible

- De générer des multitudes de fréquences infiniment variables dont la finesse du « pas » (variation) sera fonction de la précision du diviseur

- De générer des fréquences bien supérieures à celles que peut traiter la PLL, qui reste un circuit logique généralement limité à 12 ou 15 MHz (voir légèrement plus, mais jamais une PLL ne pourra comparer directement un signal VCO de 200 MHz par exemple).

- et surtout de générer des fréquences quasi impossibles à "fabriquer" avec un quartz (fondamentales de l'ordre du GigaHertz par exemple), tout en garantissant en sortie une stabilité équivalente à celle de l'horloge de référence, donc celle du quartz

Le « feed back » qui génère la « sortie » en tension qui à son tour fait varier la capacitance de la diode Varicap doit être « lissé » -filtré-, généralement avec un condensateur, de manière à ce que le redressement du fameux « signal de sortie à rapport cyclique proportionnel au delta de fréquence » (ouf !) ne soit pas trop minable et bourré d’accidents. De cette manière, la diode varicap ne recevra pas de brusques variations de tension à chaque impulsion de signal carré, qui auraient pour effet de provoquer une gigue de fréquence totalement incontrôlable. Sans cette cellule de redressement/filtrage, la PLL deviendrait folle, tentant sans fin de corriger la fréquence du VCO en expédiant des impulsions qui déstabiliserait encore plus ledit VCO. La cellule de filtrage est donc un "amortisseur" dont l'inertie a tendance à stabiliser la fréquence et limiter les à-coups nerveux émis par la PLL.

Revers de la médaille, l'inertie de cette cellule de redressement et de filtrage impose un temps non négligeable pour que la tension appliquée à la varicap puisse changer rapidement (si l'on veut passer, par exemple, de RTL à FIP immédiatement). Ce qui fait que le temps de « verrouillage » de la PLL est « long ». Ce temps de verrouillage est le temps nécessaire à ce que la tension correspondant à la fréquence "F" envoyé par la PLL soit atteinte (temps amorti par la charge du condensateur). Bref, y’a du retard, un retard qui a pour nom la « constante d’intégration ».

Il y a un moyen d’accélérer la monté en tension de la varicap : c’est en « tamponnant » le signal de sortie de la PLL avec un ampli op monté en intégrateur. L’ampli op ira toujours plus vite qu’une cellule R/C. Du coup, la PLL se verrouille plus vite.

Donc, si l’on n’est pas pressé (en fait, si l’on souhaite ne générer qu’une fréquence qui ne variera jamais, de 2 GHz par exemple), une PLL avec une boucle « diode-résistance-condensateur » suffit amplement. La constante de temps peut être longue –plusieurs secondes- elle ne dérangera pas l’utilisateur. Mais dans le cas d’un générateur de tracking ou d’un changement de fréquence d’auto-radio, il est préférable d’utiliser une boucle active avec un ampli op.

Les PLL ont cependant quelques inconvénients. A commencer par une électronique complexe et pas franchement amusante à calculer (surtout lorsque la boucle est « active »). L’on tente de remplace ces circuits par des composants plus simples : pour les hyperfréquences, des billes de Yig, pour des fréquences plus basses des VCXO commandés par bus I2C, des synthétiseurs de fréquences « directes »( DDS) etc.

D’autre part, le signal d’une PLL n’est pas d’une pureté spectrale extraordinaire, et le signal généré est souvent entaché d’un bruit de phase important. Une partie de ce bruit est d'ailleurs provoqué par la présence de l'ampli op dans la boucle de verrouillage de phase. Ce qui nous amène à une seconde conclusion d'utilisation : si l'on n'est pas contraint par des nécessité de changement de fréquence rapide, entre une pll active et une pll passive, il sera toujours préférable d'opter pour la conception d'une pll passive, légèrement moins bruyante.

Cette rapide description ne serait pas complète si l’on oubliait de mentionner certaines astuces simples. Sans entrer dans les détails mathématiques de calcul de boucle d’intégration, il apparait que plus le « pas » d’un synthétiseur de fréquence à base de pll est fin, plus la stabilisation de la boucle est délicate et longue… et sujette au bruit. Régler une fréquence à 0,01Hz relève de l’exploit avec des moyens amateurs.

Il existe pourtant une astuce de contournement. S’il est difficile de diviser finement une fréquence à synthétiser, il est en revanche très simple de modifier la fréquence du quartz de référence. La PLL étant persuadé que la référence est immuable, elle en suivra la moindre variation en croyant que la différence de fréquence est de la faute du VCO et corrigera d’autant la tension à appliquer sur la diode varicap. Hors, pour faire varier la fréquence d’un quartz, il suffit d’un simple condensateur variable. Mieux encore, tout en conservant la stabilité du quartz, rien n’interdit de monter en guise d’horloge de référence une série de quartz montés en parallèle et en mode « super VXO ». Un tel montage autorise un décalage en fréquence de près de 200 à 250 KHz autour de la fréquence centrale du quartz sans nuire à la stabilité de l’ensemble. Le diviseur de la pll n’a plus qu’à s’occuper de la variation par pas de 200 kHz, ce qui ne pose aucune difficulté d’un point de vue technique et évite même parfois de recourir à une boucle active.

Synthèse numérique directe - DDS

La synthèse numérique directe est une méthode pour constituer des synthétiseurs de fréquence en exploitant le traitement numérique de signal.

Contrairement aux synthétiseurs classique utilisant une PLL, il n'y a pas de boucle d'asservissement et les problèmes de bruits de phase qui lui sont associé absent. Le signal étant généré numériquement, il n'y a pas les aléas de l'analogique et la stabilité en fréquence dépend donc uniquement de précision et stabilité de la fréquence de référence.

Pour des fréquences très faible il est possible de généré une signal par logiciel depuis un PC ou microcontroleur, cependant pour l'utilisation RF, il existe des circuits spécialisés. Analog device propose des composants fonctionnant jusqu'à quelques centaines de mégahertz avec une résolution inférieur au Hertz. Ces circuits spécialisé intègre un convertisseur numérique/analogique pour fournir une sinusoïde à plusieurs dizaine de Mégahertz dans le cas d'une utilisation directe.

Il est également possible d'utiliser le DDS comme référence de fréquence pour une PLL (Cas de l'analyseur décrit). Ce système permet d'obtenir une grande résolution, bien meilleur que celle fournit par les diviseurs de la PLL. Dans ce type d'utilisation, il est préférable d'exploiter la sortie carré plutôt que sinusoïdale, tel est la convenance du comparateur de phase. Comme dans tout système utilisant le traitement numérique du signal, la limite théorique de la fréquence maximal est Fe/2 (Théorème Nyquist-Shannon), soit dans le cas d'une horloge à 64MHz : 32MHz. Au delà un phénomène de repliement de spectre se produit.

En plus de la limitation en fréquence de ce type de synthétiseur, un grand nombre d'harmonique sont produit par le convertisseur numérique analogique, ce qui nécessite un filtre passe bas en sortie. Ceci est d'autant plus vrai que le signal de référence a tendance à se retrouver dans le signal de sortie.