Projets:Perso:2018:VNARefit

Contents

VNA Baseband 2-12GHz

Le but de ce projet est de réutiliser certains vieux testsets de VNA (notamment ceux présents dans la baie R&S). La carte vise à remplacer les unités d'affichage et de calculateur. Seul les coupleurs/pont de reflectométrie sont gardés. La carte embarque aussi les PLL nécessaires pour remplacer les générateurs de balayage.

La documentation de ce projet se découpe en différentes parties, d'abord une partie diagramme avec explications détaillées et enfin les fichiers de fabrication (kicad) avec le code FPGA et PC.

Le git sera bientôt migré sur celui de l'electrolab.

Détails d'architecture

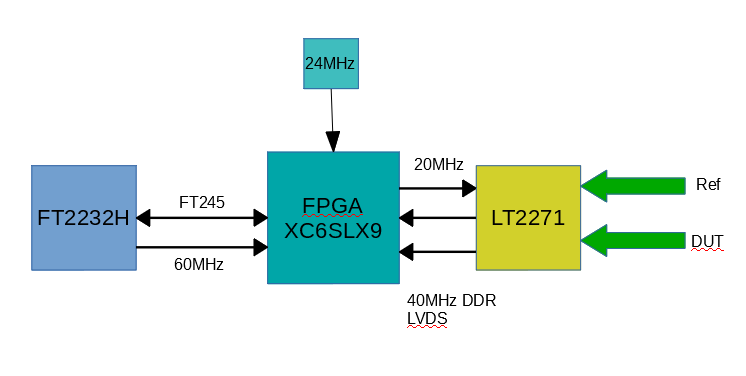

Partie Numérique

La partie numérique est somme toute relativement classique, il s'agit d'un [Spartan 6] de Xilinx (sera sans doute remplacé par un Spartan 7 à terme) accompagné d'un [FT2232H] de FTDI. Le FT2232H est utilisé en mode FT245 Synchrone. Les contraintes de latence et de débit instantané sont assez faibles dans l'usage prévu, en effet l'acquisition des échantillons se fait à la demande par paquet. Une architecture différente sera nécessaire si il est envisagé d'utiliser la carte comme un récepteur radio de 2 à 12GHz.

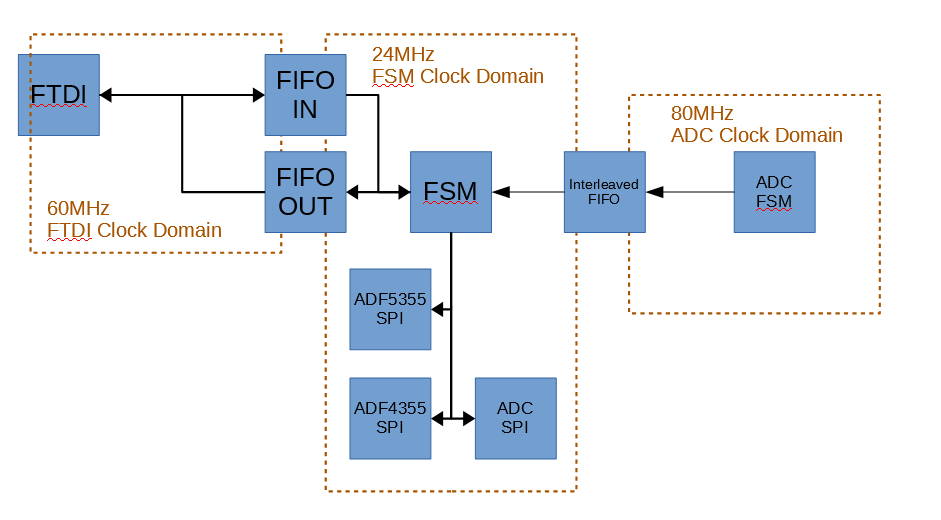

Le premier jet du HDL est écrit en Verilog, mais une version définitive est prévue en SpinalHDL. Cette première version ne contient pas de softcore, il s'agit juste d'une FSM récupérant les commandes venant de l'USB et pilotant les PLL et l'ADC. La principale "difficulté" de cette architecture est d'avoir 3 domaines d'horloges différents non alignés. Tous les échanges de données sont donc réalisés au travers de FIFO.

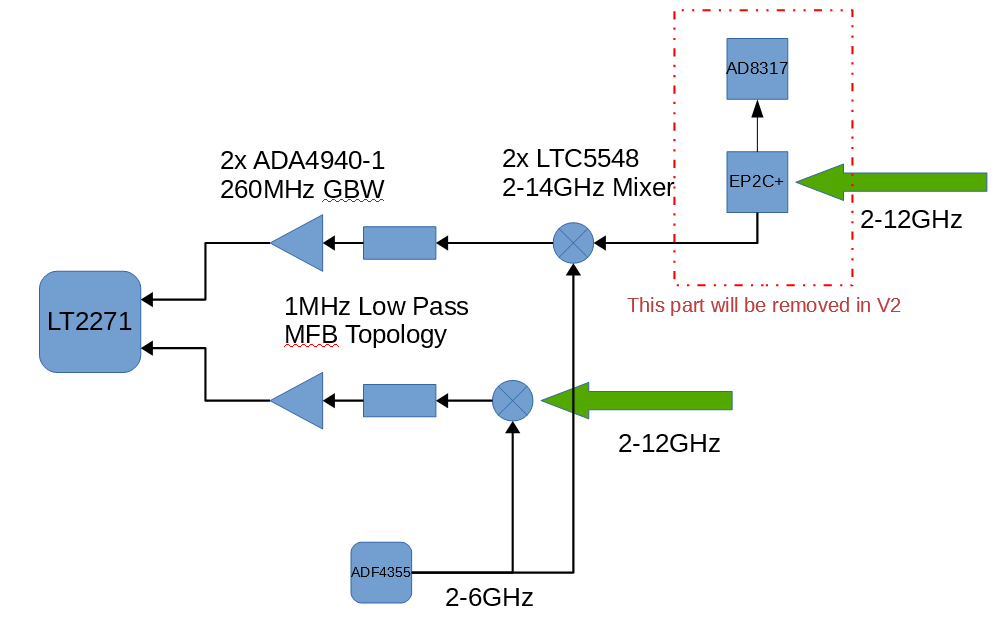

Entrées Analogiques

La partie analogique du projet sera sans doute modifiée de manière significative pour la V2 du projet (Oui il y aura une V2 :p) en effet le détecteur log va être enlevé du système (et donc le splitter Mini-Circuit aussi). Les problèmes introduits par ce système, ainsi que la perte de dynamique, ne se justifient pas par la fonction réalisée. La mesure de puissance de la référence se fera donc de manière numérique.

La présence d'un doubleur activable à la demande sur l'entre LO du LTC5548 permet de ne router que du 6GHz sur cette partie de la board et aussi d'utiliser une ADF4355 en lieu et place d'une ADF5355.

La V2 embarquera aussi une ADF5355 pour générer le signal de test (balayage de 2 à 12GHz).

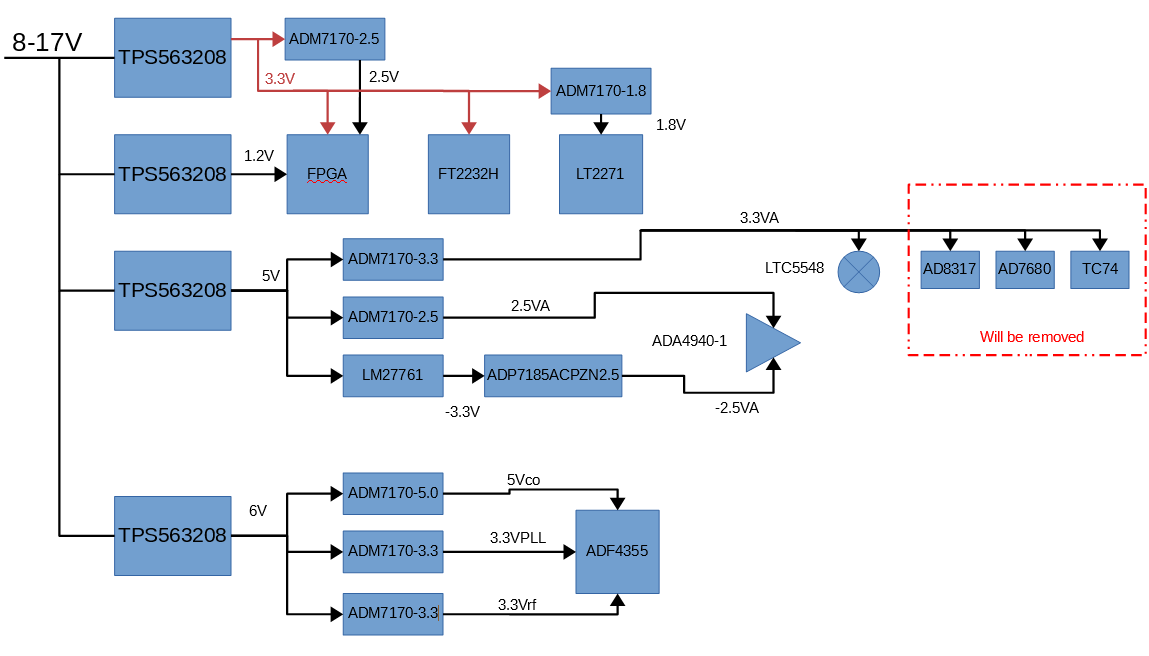

Arbre d'alimentation

L'arbre d'alimentation est plutôt classique. Quelques optimisations peuvent être réalisées pour la prochaine révision.