Difference between revisions of "Projets:Perso:2013:Carte MAX7000"

(Création de la page) |

(Description détaillée) |

||

| Line 1: | Line 1: | ||

= Introduction = | = Introduction = | ||

| − | L'idée de départ était de faire une carte qui réutiliserait les MAX7000 récupérés et servirait de support matériel à une formation au VHDL et | + | L'idée de départ était de faire une carte qui réutiliserait les MAX7000 récupérés et servirait de support matériel à une formation au VHDL et à la logique programmable. |

| + | |||

| + | = Cahier des charges = | ||

| + | (Oh quel titre pompeux !) | ||

| + | |||

| + | De quoi a-t-on besoin sur ce genre de carte ? Des entrées/sorties, une horloge, un reset, une alim. C'est vite réglé. En détail, ça donne: | ||

| + | * Une entrée d'alimentation 5V, deux régulateurs LDO pour générer les 3,3V et 1,2V nécessités par le CPLD | ||

| + | * Un circuit de reset à la mise sous tension + un bouton poussoir | ||

| + | * Un oscillateur, 16MHz par exemple | ||

| + | * Des connecteurs pour permettre de se brancher sur les entrées/sorties du CPLD | ||

| + | * Un connecteur JTAG pour programmer le CPLD | ||

| + | |||

| + | = Le schéma = | ||

| + | Rien d'extraordinaire, on retrouve les blocs décrits dans le cahier des charges | ||

| + | |||

| + | [[File:max7000_schema.png]] | ||

| + | |||

| + | Il y a une entrée pour un signal d'horloge, un jumper permettant de choisir entre l'oscillateur de la carte et l'horloge externe | ||

| + | |||

| + | Chaque alimentation (5V externe, 3,3V et 1,2V) a sa LED témoin. Une quatrième LED est connectée à l'une des sorties du CPLD. | ||

| + | |||

| + | Les connecteurs d'entrée/sortie sont à 2 rangées de 8 contact. Ils sont associés à des connecteurs à 1 rangée de 8 contacts tous reliés à la masse. | ||

| + | |||

| + | = Le circuit imprimé = | ||

| + | L'ensemble tient sur une carte de 10cm x 6 cm | ||

| + | |||

| + | [[File:max7000_pcb.png]] | ||

| + | |||

| + | En haut à gauche, le connecteur d'alimentation. En dessous, les deux régulateurs et tout en bas le connecteur JTAG. | ||

| + | Au milieu, le CPLD avec les connecteur d'entrées/sorties en haut en bas. | ||

| + | |||

| + | En haut à droite des connecteurs un petit connecteur regroupe le reset, une seconde entrée d'horloge et un signal global de mise en haute impédance des entrées/sorties du CPLD (à confirmer, j'ai un doute). Encore plus à droite, un connecteur BNC pour l'entrée d'horloge, en dessous l'oscillateur et entre les deux à gauche le jumper de choix de la source d'horloge. | ||

| + | |||

| + | Enfin en bas à droite, le bouton de reset. | ||

| + | |||

| + | = Réalisation = | ||

| + | Rien n'a encore été fait mais si assez de gens manifestent de l'intérêt pour la chose ça pourrait changer | ||

Revision as of 00:53, 25 April 2013

Introduction

L'idée de départ était de faire une carte qui réutiliserait les MAX7000 récupérés et servirait de support matériel à une formation au VHDL et à la logique programmable.

Cahier des charges

(Oh quel titre pompeux !)

De quoi a-t-on besoin sur ce genre de carte ? Des entrées/sorties, une horloge, un reset, une alim. C'est vite réglé. En détail, ça donne:

- Une entrée d'alimentation 5V, deux régulateurs LDO pour générer les 3,3V et 1,2V nécessités par le CPLD

- Un circuit de reset à la mise sous tension + un bouton poussoir

- Un oscillateur, 16MHz par exemple

- Des connecteurs pour permettre de se brancher sur les entrées/sorties du CPLD

- Un connecteur JTAG pour programmer le CPLD

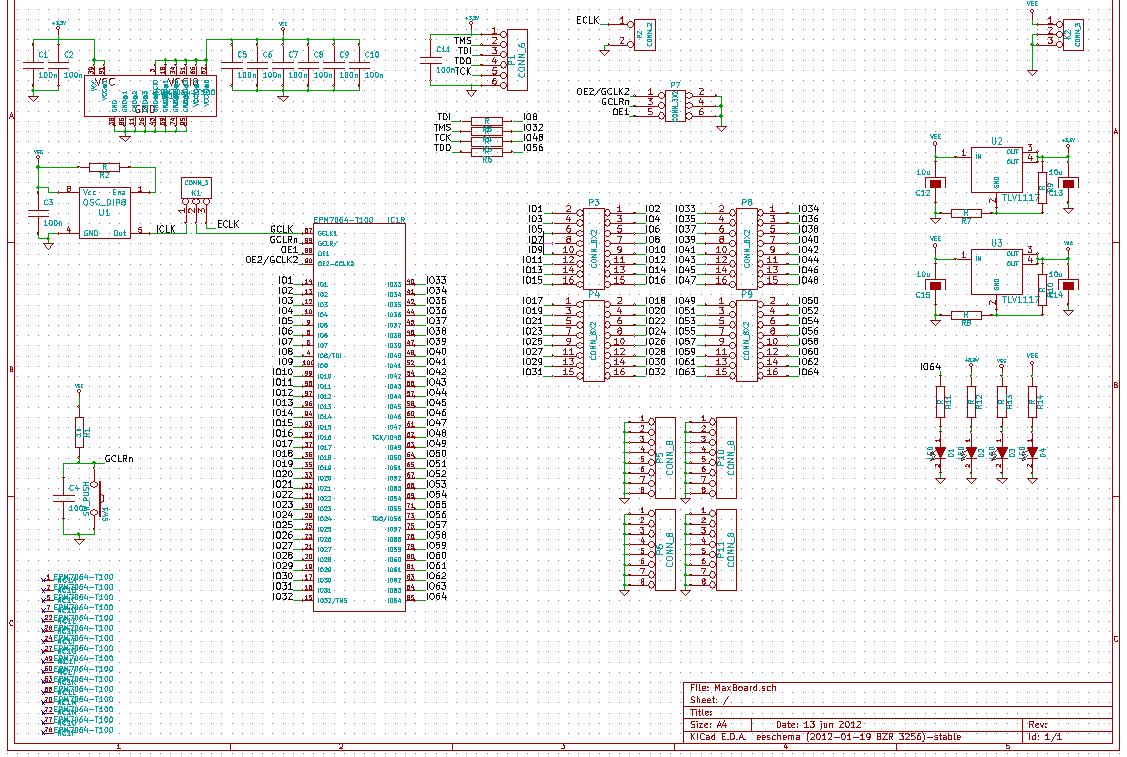

Le schéma

Rien d'extraordinaire, on retrouve les blocs décrits dans le cahier des charges

Il y a une entrée pour un signal d'horloge, un jumper permettant de choisir entre l'oscillateur de la carte et l'horloge externe

Chaque alimentation (5V externe, 3,3V et 1,2V) a sa LED témoin. Une quatrième LED est connectée à l'une des sorties du CPLD.

Les connecteurs d'entrée/sortie sont à 2 rangées de 8 contact. Ils sont associés à des connecteurs à 1 rangée de 8 contacts tous reliés à la masse.

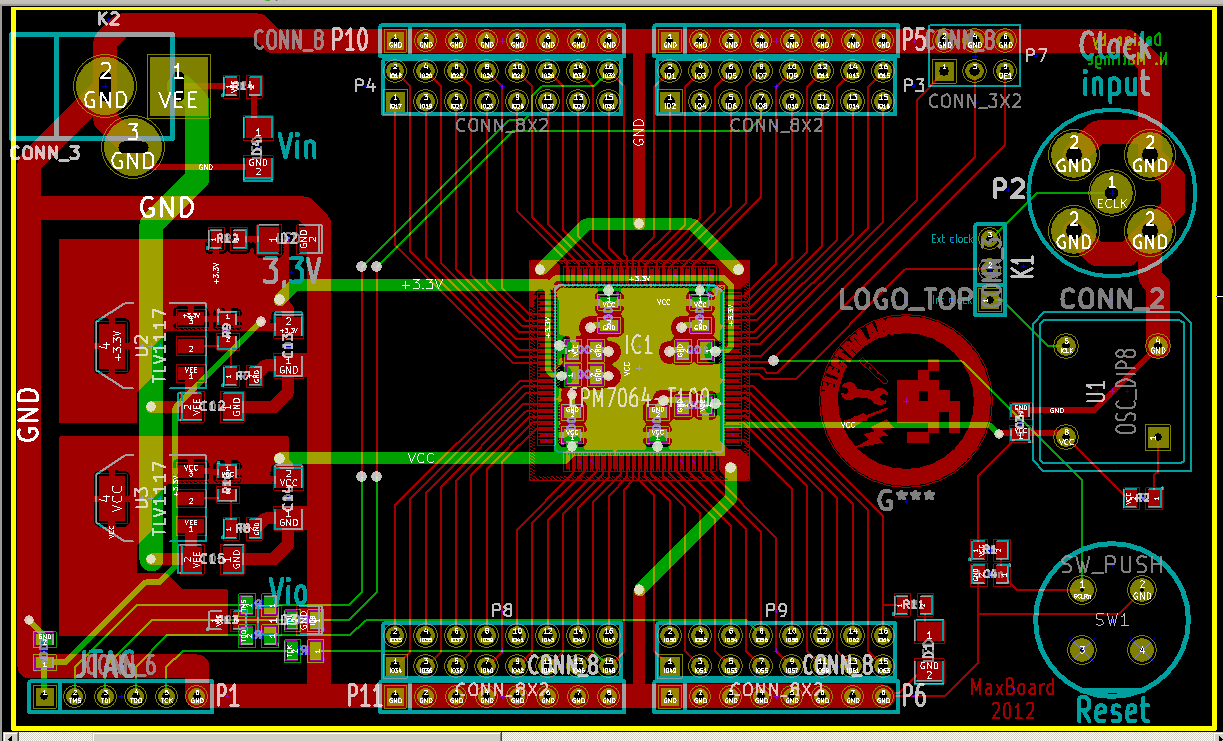

Le circuit imprimé

L'ensemble tient sur une carte de 10cm x 6 cm

En haut à gauche, le connecteur d'alimentation. En dessous, les deux régulateurs et tout en bas le connecteur JTAG. Au milieu, le CPLD avec les connecteur d'entrées/sorties en haut en bas.

En haut à droite des connecteurs un petit connecteur regroupe le reset, une seconde entrée d'horloge et un signal global de mise en haute impédance des entrées/sorties du CPLD (à confirmer, j'ai un doute). Encore plus à droite, un connecteur BNC pour l'entrée d'horloge, en dessous l'oscillateur et entre les deux à gauche le jumper de choix de la source d'horloge.

Enfin en bas à droite, le bouton de reset.

Réalisation

Rien n'a encore été fait mais si assez de gens manifestent de l'intérêt pour la chose ça pourrait changer