Formations:PCB:Routage

{Notes de l'auteur : cette page est un draft. Il est nécessaire de la compléter, Sur le fond avec ce que j'aurais omis (en particulier en CEM car je suis une b*te en CEM) Sur la forme en faisant de la mise en forme et en mettant des exemples visuels le cas échéant. }

Contents

Routage et conception de circuits imprimés

En présupposant une connaissance de base de l'électronique, de la saisie schématique, de l'utilisation d'un logiciel de CAO électronique (Kicad, Altium, Orcad ...) et de la fabrication de circuits imprimés, cette formation aborde:

- La préparation d'un circuit avant de passer au routage

- Les bonnes pratiques

- Les méthodes "classiques" permettant de réaliser un routage de qualitay sans (trop) de douleur

- Les attendus pour réaliser un dossier de fabrication qui ne sera pas rejeté par le fabricant de PCB / qui ne sera pas raté quand fabriqué en DIY

Glossaire

- via : connection entre deux couches, c'est un trou dansune couche d'isolant, qui permet de relier deux couches de cuivre ensemble. Il existe deux façons de faire des vias. Soit percer un trou, passer un fil et souder sur le cuivre des deux côtés (via traversant), soit percer un trou et métaliser entre les deux couches pour faire le contact (via métallisé). Les vias traversants ne nécessitent pas de process particulier, par contre il faut souder toutes les connections à la main, et ces vias "dépassent", donc on ne peut pas mettre de composants dessus. Les vias métallisés nécessitent une étape de métallisation, qui est compliquée à mettre en oeuvre, par contre le process est global (on ne le fait qu'une seule fois), et les vias n'affleurent pas de la surface du cuivre, donc on peut mettre des composants par-dessus. Les vias borgnes (blind via) sont des vias métallisés qui ne débouchent que d'un seul côté du PCB (uniquement sur les PCB > 2 couches). Les vias enterrés (burried via) sont des vias qui ne débouchent d'aucun côté, et sont donc uniquement entre des couches internes.

- MCU : Micro Controller Unit, microcontrolleur, qu'on différencie de CPU, Central Processor Unit, qui n'a pas de prériphériques.

- FPGA : Field Programmable Grid Array, composant logique programmable.

- stackup : agencement des différentes couches d'un circuit imprimé (nombr, disposition, épaisseurs, matériaux).

- prepreg : nom couramment utilisé pour définir l'isolant entre deux couches de cuivre.

- substrat : définit le type de matériau utilisé pour le prepreg. Par exemple : FR1 (papier imbibé époxy), FR2 (bakélite), FR4 (fibre de verre imbibée résine époxy), etc.

- couche : un couche contient un type de matériau : cuivre, vernis, prepreg, sérigraphie ... Dans el logiciel de CAO, il y a plus de couches "virtuelles" que de couches "physiques" sur le PCB final.

- PCB : Printed Circuit Board, circuit imprimé.

- Refusion / vague : méthode de soudure. Refusion (reflow) : on applique une pâte (pâte à braser) à base d'étain mélangé à des solvants sur les zones à souder, on pose els composants dessus, on passe le tout dans un four (four à refusion / reflow oven), ce qui évapore les solvants et soude l'étain. Soudure à la vague (wave soldering) : on propulse de l'étain en fusion sur les soudures, soit sous forme d'un rideau d'étain (pour souder toute la carte d'un coup), soit localement avec une buse. La refusion est préférable (plus économique, moins de contraintes sur le routage), la vague est un process plus ancien.

- vernis épargne : vernis isolant de protection qui est appliqué sur le PCB gravé pour le protéger de la corrosion. En général bleu ou vert.

- Locating / mires : repères visuels sue le cuivre pour permettre aux outils de s'aligner sur les cartes grâce à des caméras.

- netlist : fichier contenant la description symbolique du circuit, la liste des composants et les nets les connectant entre eux.

- net : connexion électrique entre plusieurs points.

- designator : numéro unique qui identifie un composant du schéma. Il a en préfixe une lettre, correspondant au type de composant (R pour résistance, C pour condensateur ...), et en suffixe un numéro unique (R1, R2, R3 ...).

- net tie : composant "fictif" servant à relier ensemble deux nets de noms différents sans créer de conflit dans la netlist. Ce type de composant est utilisé pour permettre d'avoir des diamètres de pistes différents sur un même net (étant donné que le diamètre des pistes est lié au net quand on route en suivant les règles).

- chevelu : affichage des nets / connexions entre les pattes des composants quand les pistes ne sont pas encore dessinées. Chaque net est représenté par un trait droit, généralement gris.

- locating

- fiducial

- board cutout / board edge

- polygon pour

- etc <A remplir !>

- Top / Bottom : noms des deux couches extérieures du PCB. Le fait d'être "au-dessus" (top) ou "en-dessous" (bottom) est totalement arbitraire et conventionnel.

Rappel du flow de conception

- Conception du circuit

- Saisie du schéma

- Annotation des composants

- Association des empreintes

- Création de la netlist

- Importation de la netlist

- Création du PCB / routage

- Génération du dossier de fabrication

Pour cette formation, on part du principe qu'on a un schéma saisi et annoté. On part de l'association des empreintes.

Le schéma ne contient que des symboles, comportant des pins (des pattes de connexion) reliées entre elles par des nets (fils). Cette description du circuit est contenue dans la netlist. Le routage consiste à dessiner les empreintes des composants, puis les relier par des pistes en cuivre qui correspondent aux nets. Ces dessins sont fait en deux dimensions, sur plusieurs couches de cuivre isolées entre elles, sauf en certains points particuliers qu'on appelle des vias. La formation actuelle ne parle pas de l'utilisation du logiciel de routage, mais uniquement des techniques de routage.

Préparation du routage

Avant même de commencer à router, il y a certaines pratiques à appliquer sur le schéma pour faciliter le routage. Quelques conseils en vrac.

- Séparer les fonctions monolithiques dans des pages, et utiliser les pages hiérarchiques. Ça permet de mieux séparer les fonctions et ça rend le schéma plus lisible. Tâcher autant que possible d'avoir le moins de signaux aux interfaces des pages hiérarchiques.

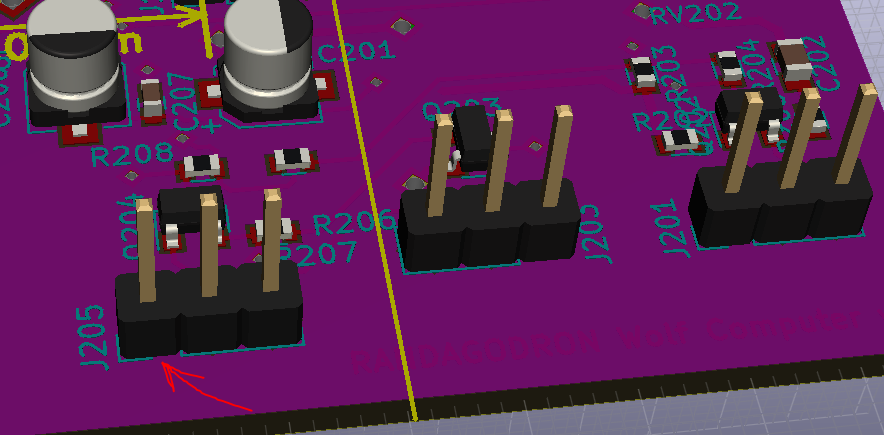

- Une fois le point précédent appliqué, à l'annotation, cocher l'option pour avoir un digit par page. Cette option signifie que, au lieu de compter les composants en strict absolu, dans chaque page les composants seront numéroté à partir d'un nombre défini. Lorsque vous avez plusieurs pages dans votre schéma, les composants de la page 1 seront annoté à partir de 100 (R100, R101, R102 ...), les composants de la page 2 à partir de 200, les composants de la page 3 à partir de 300, etc. On peut choisir de compter par centaines, voire par milliers, si le schéma complet fait plus que 10 pages, ou s'il y a plus de 100 composants d'un même type / préfixe dans une page. Cette option est très efficace, car, une fois les empreintes importées sur le PCB, le designator du composant permet de savoir immédiatement sur quelle page du schéma il se trouve, ce qui facilite l'identification et le regroupement.

- Net tie : utiliser les net tie pour séparer les chemins de puissance et de signal sur une piste de puissance, par exemple sur une alimentation distribuée à plusieurs composants ayant des consommations élevées ou très disparates, ou bien pour séparer le chemin du courant du chemin de mesure (exemple: mesure sur un shunt). Les net tie sont forcément sur le schéma et peuvent être contraignants sur la saisie. Il faut les prévoir à l'avance, le plus tôt possible dans la saisie du schéma, pour s'éviter des pertes de temps par la suite.

- Si le logiciel le permet (Altium par exemple), mettre les contraintes de routage déjà identifiées sur les signaux du schéma. Par exemples : lignes différentielles, lignes de puissance ...

- Si vous voulez ajouter des empreintes qui ne sont pas des composants (exemple : vis de fixation, logo ...), créer un symbole pour ces éléments et y associer les empreintes voulues. Il est possible d'ajouter manuellement des empreintes qui n'ont pas d'existence dans la netlist, mais c'est une mauvaise idée, s'il y a mise à jour de la netlist en cours de routage (because modif impromptue sur le schéma) il y a un risque que ces empreintes soient supprimées.

Association des empreintes Chaque symbole de composant du schéma doit être associé à une empreinte, sinon il n'existera pas sur le PCB. Les empreintes sont définies par les boîtiers choisis pour les composants. Le choix des boîtiers n'est pas innocents et doit être fait - sauf cas extrêmes - avant le routage.

Pour chaque composant, le nombre de pattes de l'empreinte doit être exactement le même que le nombre de pattes du symbole. C'est pour cela qu'un schéma en vue d'un routage n'est pas le même qu'un schéma en vue d'une simulation. L'approche doit partir du boîtier du composant : pour chaque patte physique du composant, il DOIT y avoir une patte sur le symbole.

A noter que plusieurs pattes d'une empreinte peuvent être reliées à une seule patte du symbole (courant sur les composants de puissance, les alimentations des MCU / FPGA ...).

- Vérifier les empreintes : il ne faut pas qu'il y ait d'erreur sur les dimensions, le nombre de pattes, le pinout (pinout = correspondance entre les patte fonctionnelles du symbole du schéma et les pattes physiques du boîtier du composant). S'il y a des erreurs à ce niveau:

- Il est fort probable que ça ne soit pas vu au routage, et donc on va fabriquer une carte qui ne marchera pas, vu que les signaux ne seront pas connectés correctement.

- Si une erreur est vue au niveau du routage, il est fort probable que ce soit très (trop) tard, ce qui va forcer à reprendre une partie potentiellement non-négligeable du routage, donc fatigue et perte de temps.

A vérifier : dimensions des pads, écartement des pads, diamètres des trous et des pastilles, isolations. Et tant qu'on y est, au-delà des pads et des pastilles, ça vaut le coup de prendre le temps de dessiner sur les couches mécaniques le contour de l'enveloppe physique complète du boîtier, pour que, une fois sur le routage, on sache combien de surface le composant va prendre, et éviter de trop le rapprocher d'un autre et de se rendre compte en soudant les composants que ça ne passe pas parce que les composants ramponnent.

A noter qu'il faut se méfier, pas uniquement des empreintes, mais aussi - et surtout - des symboles. Quand les empreintes sont attachées à la netlist, ce sont les numérotations des symboles du schéma qui sont prises pour faire le pinout. Se méfier car sur les symboles, chaque pin à un numéro ET un nom. Or, il peut arriver que les deux soient mélangés. Il faut bien vérifier que les numéros des pins sur le symboles soient bien les bons numéros des pins physiques sur les boîtiers.

Exemple typique (c'est du vécu) : les symboles de transistors dans les librairies fournies par Kicad. Je mets un BC850 sur le schéma, le symbole est dans la lib "transistors" de Kicad. J'y attache le boîter que je veux y attacher : SOT-23 (CMS). Pour info, les transistors bipolaires en boîtier SOT-23 ont TOUJOURS le même pinout (c'est une exception rare). Une fois la carte fabriquée, le circuit ne marche pas, le pinout n'est pas bon. Je vérifie le pinout du symbole : ils ne correspondent pas à un transistor bipolaire en SOT-23, en effet les numéros des pins sur le symbole de la lib Kicad correspondent au pinout du BC850 en boîtier TO-8 (traversant), boîtier qui n'est pas normalisé, et dont le pinout peut changer d'un modèle de transistor à l'autre. CQFD.

- Check la netlist : vérifier qu'il n'y a pas des nets reliés à un seul composant (sauf antenne, évidemment), vérifier qu'il n'y a pas de nets qui ont des noms proches, mais pas exactement les mêmes (fautes de frappe au niveau de labels, très courant). Pour cela le DRC peut faciliter (DRC = Design Rule Check, c'est un outil du logiciel de CAO qui fait des vérifications et rapporte les résultats. Un DRC doit être réglé pour détecter les erreurs pertinentes, c'est un peu pénible à faire mais ça peut valoir le coup d'y passer un peut de temps).

- Identifier les nets d'alims et de puissance, savoir combien on doit passer de courant pour pouvoir calculer la largeur de psite requise. Si on même net a plusieurs branche dont certaines avec de la puissance et d'autres pas (exemple : alimentation d'une charge de puissance + lecture de la tension par un shunt), utiliser des net-tie pour séparer les "domaines" de courant. Idéalement il faut utiliser les fonctions de directives si elles sont disponibles dans le logiciel de CAO (Kicad n'en a pas nativement) et assigner des largeurs de pistes dans le schéma, pour que ça soit pris en compte au routage. Sinon au minimum noter le nom des nets pour savoir lesquels doivent avoir une largeur différente du standard.

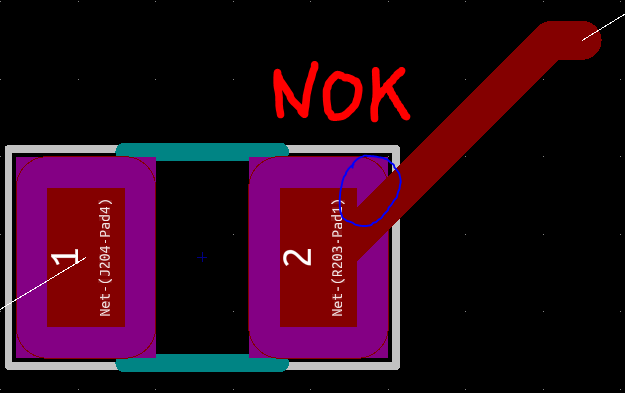

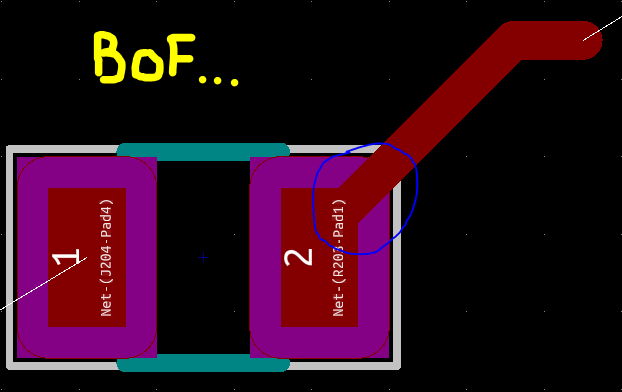

<photo BAB>

Paramètre important, mine de crayon. Moins il y en a et plus c'est facile à fabriquer, mais plus c'est potentiellement compliqué à router. Le problème que l'on peut rencontrer quand il y a peu de couches, c'est qu'il peut y avoir tellement de pistes qui se croisent dans tous les sens que ça ne passe plus et qu'il devient impossible de finir le routage sans faire des circonvolutions ou des sauts de couches à répétition. Il est préférable de définir le nombre de couches avant de router, pour pouvoir définir le bon nombre de couches quand on créé le fichier PCB dans la CAO.

Simple couche : avec des composants traversants ça ne pose pas trop de problème de router en simple couche, vu qu'on peut passer des pistes sous les composants. Si il y a blocage, on peut utiliser des straps, soit des fils, soit - pour les plus riches - des résistances 0 ohms. En pratique ça va se passer comme ça : on va router des pistes sur une autre couche, même si à la fin on ne fabrique que la couche principale, et toutes les pistes qui seront sur la couche supplémentaire seront en fait des fils qu'on soudera à la main. Dans ce cas-là:

- Soit on est un cochon et on tire les piste n'importe comment et les fils vont être dans tous les sens sur la carte finale,

- Soit on est un gros cochon, et pour se permettre de croiser des fils on utilise plusieurs couches supplémentaires, et on a un spagetti de fils au dos de la carte - spaghetti qui s'emmêlera avec les composants, cela va de soi,

- Soit on est un être humain civilisé et on fait bien attention à ne tirer ces pistes que à 90° (horizontales, verticales), comme les composants, et à ne faire qu'un trait à chaque fois.

- Soit on est un esthète, et l'on prend garde de ne pas tirer ces pistes sous un composant - pour faciliter le montage - et l'on prend soin d'avoir toujours la même longueur de piste, de la longueur d'une résistance, de façon à pouvoir monter une résistance 0 ohms à la place d'un fil.

A noter qu'il est très risqué de router en simple couche avec des CMS. Il est très probable de se retrouver bloqué, car peu de composants CMS permettent de passer des pistes entre leurs pattes. C'est possible dans certains cas, mais il est difficile de prévoir à l'avance si ça va passer.

A noter aussi que les logiciels de CAO ne travaillent que avec un nombre de couches pair. Donc même si on veut fabriquer un PCB simple couche, e logiciel aura une deuxième couche.

Double couche : beaucoup plus confortable que le simple couche au routage, mais plus difficile à fabriquer (si on fabrique soi-même). En double couche, si on applique les bonnes méthodes de routage (voir plus bas) il est quasiment impossible de se retrouver bloqué.

Au-delà : les PCBs multi-couches sont très difficiles à fabriquer en DIY, donc on passera par un fabricant industriel. Le nombre de couches est toujours pair, et peut monter très haut (16 couches, 20 couches, 24 couches ...), mais il faut savoir rester raisonnable, car le coût, l'épaisseur du PCB et la complexité du routage vont exploser. A partir de 4 couches il est recommandé d'avoir des couches dédiées alim / masse, sur lesquelles on va avoir des plans de masse, les pistes d'alim - distribuées sur toute la carte - et idéalement aucun signal. Ne pas router les masses, et router les alims sur une piste dédiée va déjà fortement simplifier le routage car ce sont des nets qui sont distribués un peu partout sur la carte et donc sont vite impossibles à router. Idéalement il faut avoir des couches masses avec uniquement un plan de masse - et les vias pour les connexions de masse des autres couches - de façon à faire un bel écran CEM, et les alims aussi sur une couche dédiée. Sur du 4 couches on peut tout de même avoir une seule couche masse + alims et 3 couches de signaux, ça marche aussi, mais c'est moins performant, mais sur une carte complexe ça peut sauver la mise. il est fortement recommandé de ne jamais tirer de pistes de signaux sur les couches masses ou alims. Ou alors très parcimonieusement.

On peut aussi utiliser plusieurs couches pour faire passer plus de courant dans une piste - en la dédoublant sur plusieurs couches en oubliant pas les vias qui vont avec. On peut aussi utiliser des plans de masse sur plusieurs couches pour augmenter la dissipation d'un composant de puissance dans le PCB - avec les vias qui vont aider à dissiper en augmentant la surafe de contact avec l'air et la masse de cuivre.

Tout cela pour dire qu'il faut prévoir le nombre de couche et l'assignation des couches pour définir le stackup.

Le stackup est la définition des couches : nombre, épaisseur, assignation (signal, masse, alim).

L'épaisseur des couches n'est pas en soi une exigence bloquante pour router, sauf si on fait de la HF / RF, voire de la puissance / HT, car l'épaisseur de prepreg va influer sur les capas parasites ainsi que sur l'isolation électrique. Sur des circuits BT classiques, pas la peine de s'en soucier. De plus, l'épaisseur des couches n'est pas contenue dans les fichiers générés par la CAO, et d'une façon générale, le stackup doit être donné au fabricant en-dehors du routage en lui-même. La plupart des fabricant proposent d'ailleurs des stackups "standard", que l'on peut prendre sans trop de risques.

Le nombre de couches doit être connu avant de router car on va le définir dans le logiciel de CAO, et ce n'est pas une bonne idée de décider de changer le nombre de couches en cours de routage, car on ne route pas de la même façon en simple, en double, et en multi-couches.

L'assignation des couches (signal, masses, alim, mixte) devrait préférablement être faite avant de commencer à router, de façon à appliquer tout au long du routage la "politique" choisie, ce qui garantit un routage propre et cohérent.

Il existe des bonnes pratiques et des stackups "classiques" qui marchent bien. En voici quelques uns:

Simple couche:

- Composants et straps sur le top, pistes sur le bottom, et on route sur le bottom. De toutes façons, il n'y a pas d'autre façon de faire en simple couche.

Double couche:

- Composants et pistes sur une face, uniquement des pistes sur l'autre face.

- Composants et pistes sur une face, composants léger et pistes sur l'autre face.

- Composants et pistes sur une face, uniquement plans de masse sur l'autre face.

- Composants et pistes sur une face, uniquement plans de masse et alims sur l'autre face.

Quatre couches:

- Signaux sur les couches externes (top et bottom), une couche interne pour les alims, une couche interne pour les masses.

- Signaux sur les couches externes (top et bottom), une couche interne pour les alims et les masses, une couche interne pour les signaux.

Six couches:

- Signaux sur les couches externes (top et bottom), une couche interne pour les alims, une couche interne pour les masses, les deux couches les plus au milieu pour les signaux rapides.

Quelques liens plus précis:

PCB Stak-up intro PCB Stak-up 4 layers PCB Stak-up 6 layers PCB Stak-up 8 layers PCB Stak-up 10 layers

Une doc de conseils sur le stackup pour le routage des cartes avec des FPGAs Altera Intel (Ils ont pas perdu leur temps pour re-brander tous les docs)

Pour savoir quelle est la surface de PCB requise pour router, on utilise souvent un ratio entre la surface des empreintes et la surface routable, en excluant les connecteurs (ici par "surface des empreintes" j'entends la somme des enveloppes des empreintes de tous les composants de la carte). Sur du double face en FR4, un ratio 1.6, voire 1.5 est suffisant, ce qui signifie que le PCB doit avoir au moins 50% de surface routable en plus que la surface des empreintes des composants. Pour rester raisonnable il vaut mieux faire un ratio d'au moins 2 ou 3 (surtout si on est moins fin qu'en classe 4, ou avec des composants sur une seule face).

Exemple avec des composants CMS -> on prend la BOM en Excel, on met des valeurs arrondies, on fait la somme.

Router, en pratique, ça veut dire quoi ?

En pratique, le routage en lui-même sera effectué par l'utilisateur, le logiciel de CAO fournissant uniquement une aide pour ne pas faire de bêtise. L'utilisateur devra placer à la main chaque composants et dessiner à la main chaque piste. C'est long et fastidieux, parfois même compliqué, donc il faut l'aborder avec méthode. Les aides fournies par l'outil seront de différente nature:

- Une grille "aimantée" pour placer les composants et dessiner les pistes avec plus de facilité (et faciliter la fabrication, voir j'en reparle plus bas)

- Des pistes qui se dessinent en appliquant automatiquement les contraintes de largeur de piste et d'angle.

- Empêcher de faire des court-circuits entre pistes qui ne sont pas sur le même net.

- Empêcher de trop rapprocher des pistes ou des zones de cuivre, de façon à garantir l'isolation électrique.

- Remplir automatiquement les polygones.

- Dessiner automatiquement les jonctions particulières (freins thermiques).

- Etc ...

En fonction des logiciels, on peut configurer très finement pour mettre des contraintes automatiques très pointues : contraintes sur le placement des composants interdisant de trop les approcher les uns des autres ou des bords de carte, largeurs de piste différentes en fonction du net auquel elles sont reliées (cf. net tie), isolations différentes en fonction des nets, priorités entre les polygones pour pouvoir les superposer et créer des formes complexes facilement, etc.

Quand je dis que le logiciel "interdit" ou "empêche" une action, c'est à prendre au sens littéral : si on essaye de faire l'action, le logiciel ne la fera pas. Par exemple, si on a tiré une piste, puis que l'on tire une autre piste, sur un autre net, et qu'on essaye de la faire croiser la piste précédente, le logiciel ne dessinera pas la piste. Le dessin de la piste ne suivra pas le curseur de la souris, et soit s'arrêtera au dernier endroit possible qui ne croise pas la piste, voire va prendre automatiquement un chemin qui contourne la première piste, de façon à ne pas la croiser. C'est pour cela que l'on parle de conception "assistée" par ordinateur : il faut faire le travail soit-même, mais le logiciel aide en empêchant de faire des choses interdites.

Autorouteur, routage automatique

C'est un paradoxe dans le monde de la CAO électronique : tout logiciel de CAO se doit de disposer d'un routeur automatique, mais aucun électronicien n'acceptera jamais de l'utiliser, sous peine d'être la risée de ses confrères. En général, le résultat d'un routage automatique est moins optimisé qu'un routage fait à la main, et est généralement "pas beau". Nous, les électroniciens, on aime pas le routage automatique. C'est comme ça.

Contraintes, configuration du routage

Comme dit précédemment, le logiciel va assister le routage de façon très active. Mais il le fait en suivant des contraintes qu'il faut lui indiquer explicitement. Les contraintes sont importantes, à la fois pour se simplifier la vie pendant le routage en lui-même, amis aussi pour garantir que le routage sera conforme aux spécifications données par le fabricant de PCB. En effet, aucun fabricant de PCB ne peut fabriquer un PCB que ses machines ne sont pas capables de fabriquer. Cela peut sembler évident, mais ça fait du bien quand c'est dit. Pour mieux comprendre cela, il faut regarder ce qu'il se passe quand on fait fabriquer un PCB.

Pour faire fabriquer un PCB, on envoie à une entreprise de fabrication de PCB un dossier de fabrication. Ce dossier va contenir les fichiers définissant le circuit imprimé que l'on veut, ce qui se traduit en pratique par une liste de fichiers vectoriels dessinant les différentes couches du PCB. En fonction de ce que l'on demande, il faut que les couches requises soient présentes dans le dossier. Par exemple, si on demande une sérigraphie, il faut que la couche sérigraphie soit présente dans le dossier. Sinon, au mieux vous n'aurez pas de sérigraphie sur le PCB, mais vous aurez quand-même payé le supplément, ce qui est ballot.

Mais encore, un fabricant de PCB va utiliser des machines pour fabriquer des PCBs. Or, ces machines ont des limites, des tolérances maximales ... Les limites des machines définissent la qualité maximale que le fabricant peut obtenir. De ce fait, les fabricants annoncent ces limites, en se prenant une marge de façon à être surs de pouvoir fabriquer selon ces limites qu'ils se fixent. Ces limites sont les spécifications de fabrication.

Exemples de specs de fab' :

Quand un fabricant annonce ses spécifications de fabrication, il ne sert à rien d'envoyer un dossier dont les contraintes dépassent ces spécifications. Au mieux il refusera de fabriquer, au pire il fabriquera quand-même, il y aura des approximations et le résultat sera désastreux et ne marchera pas. Les fabricants sérieux utilisent des outils logiciels spécifiques pour tester les dossiers qu'ils reçoivent de leurs clients, et vérifient ainsi automatiquement si les dossiers dépassent leur qualité de production, avant même de fabriquer.

Donc, il faut garantir que le routage est conforme aux specs du fabricant, sinon ça va mal se passer.

En général, les specs des fabricants sont calibrées sur les normes JEDEC, de façon à ne pas perturber les clients. La plupart du temps ils annoncent quelle classe de routage ils peuvent atteindre. Plus la classe est élevée, plus les pistes sont fines et rapprochées. La plupart du temps, d'ailleurs, le tarif n'est pas le même en fonction de la classe dont on a besoin, il peut donc être intéressant économiquement de ne pas être trop gourmand au niveau finesse de gravure.

Il est à noter qu'un dossier peut se voir refuser, même s'il est généré à priori avec les bonnes règles. En effet, les logiciels de vérification des fabricants sont souvent beaucoup plus précis et pointilleux que le logiciel de CAO utilisé par le client, et il peut y avoir des détails des couches qui enfreignent les specs du fabricant. Exemple vécu : un routage fait avec Altium, refusé car il y avait des isolations non respectées à certaines jonctions entre polygones et pads. En fait, il s'est avéré qu'Altium, dans certains cas, générait mal les angles sur les polygone, ce qui faisait qu'il y avait des coins de pads de composants qui se retrouvaient trop proches du cuivre généré dans le polygone, au niveau de la pointe de l'angle du pad. Altium ne voyait aucune erreur, le logiciel du fabricant si. Je n'ai pas de règle à donner pour éviter ce cas. Ça arrive rarement, et dans des cas particuliers. Honnêtement, il faut vraiment faire des routages biscornus pour rencontrer ce genre de problèmes.

Sachant quelles sont les contraintes de fabrication, on peut maintenant les ajouter dans le logiciel de CAO, de façon à ce qu'elles soient appliquées automatiquement.

<Sous Kicad : ajout des contraintes>

Dans le logiciel de CAO en lui-même, il n'y a pas de règle universelle. Certains utilisent une netlist pour les échanges entre la saisie schématique et le logiciel de routage, d'autres pas, et cette netlist peut être plus ou moins lisible (fichier .net en plain text, ou pas). Idem pour les fichiers internes de CAO. Par contre, en sortie, le format est imposé par les fabricants de PCB ou les outils de fabrication (plotteur laser ...). La majeure partie du temps, le format dans lequel il faut générer le dossier de fabrication est le format GERBER (Wikipedia - GERBER Spec format GERBER). C'est un format vectoriel, historiquement utilisé pour les tables tables traçantes, qui est un standard de fait. Il n'y a jamais vraiment eu besoin de remplaçant et le GERBER est resté le standard par défaut. D'autres formats existent mais sont moins courants dans ce champ d'application : ODB++, GenCam, DXF ...

A noter que certains fabricants acceptent les formats des logiciels de CAO. Par exemple, Seeed accepte qu'on fournisse le fichier .kicadpcb de Kicad, directement, sans faire d'export.

On peut avoir, dans un seul et même circuit / produit, plusieurs cartes reliées par des connecteurs inter-cartes. Dans ce cas il faut faire l'architecture du circuit complet pour identifier où le découpage se fera entre les cartes, et donc où seront les connecteurs dans le circuit, et donc quelles fonctions seront sur quelle carte, et donc quels composants seront sur quelle carte.

Ce découpage est assez critique, car il doit être fait au niveau du schéma, il ne peut pas être fait à posteriori sur le routage. Sur le schéma, il faudra ajouter chaque contrepartie de connecteur sur chacun des cartes entre lesquelles chaque connecteur se trouve. Il ne faut pas se tromper dans les connections entre les signaux et les pattes des connecteurs, il faut bien faire attention que les numéros soient les mêmes sur chaque carte, et vérifier qu'on ne trompe pas de sens.

Une fois sur le routage, il faudra vérifier que les connecteurs sont bien alignés (surtout s'il y a plusieurs connecteurs inter-cartes sur une même carte) et bien dans le même sens.

D'un point de vue plus général, le découpage est critique, car il va déterminer la place occupée par les composants sur chaque carte, ainsi que la complexité des connexions. Plus il y a de signaux à faire passer sur une connexion inter-cartes, plus les connecteurs seront encombrants (et chers). De plus, une liaison à travers un connecteur est moins fiable qu'une liaison directe sur le PCB, et est limitée en puissance et en fréquence. Il faut donc éviter de faire transiter des signaux haute fréquence, des signaux d'alim, des signaux de puissance (fort courant, forte tension), des signaux sensible au bruit ou aux variations d'impédance (boucle de régulation de circuit d'alimentation, signaux à faibles niveaux et haute impédance ...).

Donc, si on fait une connexion inter-cartes, il faut se débrouiller pour y faire passer le moins de signaux possibles, et des signaux "non-critiques". Ça ne laisse pas beaucoup de possibilités ...

Sans entrer dans le détail, c'est la solution luxueuse pour éviter d'avoir des connecteurs inter-cartes. A priori, utiliser un PCB flex permet de faire le découpage au routage, sans aucune modification sur le schéma. De plus, c'est beaucoup plus fiable qu'un connecteur soudé, et ça a quasiment les même performances que le reste du PCB "pas flex". Par contre, attention aux contraintes de routage (dépendent du fournisseur), aux contraintes mécaniques (angle de flexion), et au prix !

Penser aussi au montage : les PCB flex sont nettement plus fiables que les systèmes à multiples PCBs avec connecteurs inter-cartes ... si on respecte leur specs de contraintes mécaniques ! Si l'angle de flexion une fois monté dans le boîtier n'est pas bon, le flex peut casser à terme. Et s'il faut faire des manipulations tarabiscotées pour monter le PCB dans le boîtier, on risque de casser le flex au montage.

Connections isolées (opto-coupleurs, isolateurs électriques, transformateurs)

Sans entrer dans le détail, les contraintes de ce genre de liaisons sont très proches des liaisons inter-cartes. Les isolations électriques coûtent cher, donc il faut limiter le nombre de signaux qui y sont astreintes. Sur des problématiques d'isolation électrique (et pas uniquement galvanique), la mécanique va aussi entrer en jeu, car une zone sans cuivre devra être garantie entre les zones isolées, ce qui signifie que les composants d'isolation ne pourront pas être situés n'importe-où.

D'une façon générale, il est préférable d'avoir des composants d'un seul côté du PCB, même sur un double face. Cela facilite le montage, et dans le cadre d'une carte fabriquée industriellement cela facilite le process, vu qu'il n'y a qu'une seule refusion. Si le manque de surface impose de mettre des composants des deux côtés, il aut essayer au maximum de mettre les composants "lourds" tous du même côté, et de n'avoir que des petits composants sur l'autre face (passifs, SOT-23, SO-8 ...). Si la carte doit être fabriquée industriellement, il y aura une double refusion, et à la deuxième refusion il ne faudra pas que les composants qui sont passés à la première refusion ne tombe par gravité. D'où l'intérêt de regrouper les plus lourds du même côté pour n'avoir que des composants légers sur l'autre face, que l'on fera passer en première refusion (les composants légers ne tomberont pas).

On peut malgré tout envisager de coller les gros composants avec une colle ad-hoc permettant qu'ils ne tombent pas à la deuxième refusion. Le process est plus compliqué et il faut une colle spécifique, donc c'est plus cher.

En plus des problèmes de poids cités plus haut, il faut faire attention que tous les composants passent à la refusion. Les composants "solid-state" sont compatibles en général. par contre, les composants électro-mécaniques peuvent poser problème, typiquement:

- Les relais : ce sont des enceintes confinées remplies d'un gaz inerte, certains ne peuvent pas passer en refusion sous peine de casser leur étanchéité.

- Les connecteurs : certains plastiqeus utilisés sur des connecteurs ne tiennent pas les température de refusion.

- Les switches : les pièces plastiques peuvent gripper les mécanismes

- etc.

Les composants qui ne passent pas en refusion devront être soudés à la main, ou à la vague.

Le routage

- Toujours afficher le chevelu général, ou au minimum local pour le placement, sinon on ne comprend pas ce qu'on fait.

- Autant que possible, il faut regrouper les composants par fonction. Ca permet de les traiter comme des "macro composants" et c'est beaucoup plus facile à gérer !

- Toujours utiliser la grille en "snap" ("aimantée"). Tout ce qui est dessiné sur le PCB par l'utilisateur doit être défini sur la grille, pas de placement libre, sinon c'est impossible à fabriquer. A la fin du routage, les fichiers de fabrication sont des fichiers vectoriels, qui donnent des coordonnées permettant de dessiner des formes géométriques. Il faut que ces coordonnées soient définies sur une grille correcte, sinon les outils de fabrication vont faire des arrondis, et les arrondis c'est pas bon. A vérifier sur les specs fabricant mais à priori on peut utiliser systématiquement du SI. En général, sur de la classe 4, on prend un grille de 0.25mm pour le placement des composants, un grille de 0.1mm pour le routage.

Il faut déterminer l'assignation des couches. Il faut le faire dès le début car une fois que c'est défini c'est compliqué de le changer après coup.

Choisir entre Top et Bottom n'a pas vraiment d'importance, vu que le PCB est plat, donc ça peut se retourner. La seule chose qui compte c'est que l'ordre des couches internes - si couches internes il y a - soit correct. Sauf cas particulier, les logiciels de CAO affichent le routage dans le sens du top, le seul critère pertinent pourrait donc être la facilité de lecture du routage, et donc, en général, on met la face avec les composants sur le top. En général le top est représenté en rouge, le bottom en bleu (mais on peut changer les couleurs de toutes les couches, vu que ce n'est que de l'affichage).

Dessin du contour du PCB

Comme dit précédemment, pour router une carte il faut placer les composants puis tirer les pistes. Pour cela il vaut mieux au préalable savoir quelle est la forme qu'aura la carte. Il n'est pas interdit de faire le routage, puis dessiner le contour de la carte autour après, si on n'a pas de grosses contraintes mécaniques. Si on a déjà un boîtier, ou des contraintes mécaniques, il vaut tout de même mieux dessiner le contour du PCB en premier.

- Contour / edge cut / descente de composants

- Zones méca / fixation / zones interdites / zones isolées

Si la mécanique est connue (boîtier, contraintes sur la hauteur, sur l'arrivée des connections ...), alors il faut commencer par dessiner le contour PCB (Edge cut / Board edge). Pour ça il y a plein de méthodes. De base on peut toujours dessiner "à la main" dans le logiciel, en utilisant l'outil de cotes. La méthode la plus clean consiste à dessiner le contour sous un logiciel de CAO mécanique - le même que celui où l'on dessine le boîtier, puis de l'importer dans le logiciel de CAO électronique. Par exemple, Kicad peut importer du DXF.

Il ne faut pas hésiter à utiliser les couches de "commentaires" pour mettre des indications qui aideront à router sans pour autant que ces indications se retrouvent sur le cuivre. Par exemple, sous Kicad on dispose de deux couches "user" et d'une couche de commentaires. Personnellement j'utilise toujours la couche user 1 pour dessiner le contour du PCB (je mets les cotes et les traits de guidage), et la couche user 2 pour les éléments internes à la carte (cotes pour le placement des connecteurs, zones interdites, zones fonctionnelles ...). Une autre approche serait d'utiliser une des couches pour mettre toutes les cotes, et l'autre pour dessiner toutes les indications. Comme ça on peut désactiver l'affichage de la couche avec les cotes pour y voir plus clair.

Une fois le contour mécanique dessiné, mettre les contraintes liées aux systèmes d'attache : vis et Cie, sur lesquelles on ne peut pas mettre de composants ou de pistes (pour éviter des court-circuits).

Sur tous ce qui est attaches et "retours mécaniques" sur le PCB, il faut faire attention à prendre de la marge. En effet, rien ne garantit que quand on monte la carte dans le boîtier tout s'aligne au micron près. Et même, quand on va monter la carte on peut faire des fausses manips, et casser involontairement un composant qui est trop proche d'un bord, par exemple.

Placement

Lorsqu'on importe pour la première vois les composants sur le PCB, en général ils sont balancés n'importe comment. Sur Kicad par exemple, ils sont tous empilés les uns sur les autres au même endroit, il faut donc les sélectionner un par un et les séparer. C'est chiant mais c'est comme ça. Tous les logiciels ne fonctionnent pas comme ça. Altium par exemple permet de faire un pseudo-placement automatique, qui permet d'avoir les composants les uns à côtés des autres au lieu de les avoir empilés. Ça fait sauter une étape bien rébarbative. Mieux : on peut grouper les composants par fonction et définir des "rooms", qui sont des zones sur le PCB, et il va automatiquement "trier les patates" et placer les composants en vrac mais dans leurs "room" dédiée. Une fois qu'on a descendu et séparés les composants, il vaut mieux les regrouper par fonction. Ça permet de mieux s'y retrouver. Le découpage va donner:

- Connecteurs

- Fonctions de puissance

- Alims

- MCU / FPGA / SoC / ASIC (fonctions "intelligentes")

- Toutes les autres fonctions (interfaces, modules, etc) qui seront séparées entre elles.

A partir de là on va commencer à y voir plus clair et commencer le placement.

Le placement des composants a un impact énorme sur la facilité et la qualité du routage. Il est vraiment primordial de finir le placement de tous les composants avant de tirer les pistes. Il est possible de commencer à tirer des pistes autour d'un composant pour mieux voir la façon dont s'agencerait le routage en fonction des pistes, et donc réajuster le positionnement des composants avant de tirer complétement les pistes. Mais il faut vraiment le faire localement.

Une manière de faire est de répartir les blocs de fonctions sur l'ensemble de la carte, sans forcément chercher à positionner les composants les uns par rapport aux autres dans un même bloc. Une fois les fonctions positionnées sur la carte, on peut placer les composants les uns par rapport aux autres dans les blocs de fonctions.

Mais on peut très bien faire l'inverse, ça marche aussi : travailler sur le placement des composants les uns par rapport aux autres, fonction par fonction, puis placer les fonctions les unes par rapport aux autres sur la carte.

Personnellement de préfère la deuxième méthode, car en travaillant sur chaque petit groupe de composants séparément, on optimise les distances à router, ce qui allège fortement le chevelu, et rend le tout beaucoup plus lisible. Donc, d'une façon générale, je conseille :

- Importer la netlist

- Séparer les composants

- Regrouper les composants par fonction

- Pré-placer les composants les uns par rapport aux autres dans chaque fonction, pour avoir les chemins les plus courts possibles dans chaque fonction

- Placer les fonctions sur la carte

- Réajuster le placement es composants dans les fonctions pour que ça rentre et que ça soit harmonieux

Ordre conseillé pour le placement des composants

- Connecteurs

- Composants de puissance / radiateurs

- Composants qui font de la RF

- Gros composants (beaucoup de pattes)

- Reste

- L'objectif, à l'échelle microscopique, est d'avoir les pistes les plus courtes possibles. Pour cela, il faut rapprocher le plus possible les composants qui appartiennent à la même fonction, pour que les pistes dans les fonctions soient les plus courtes possibles.

- Il est préférable d'avoir tous les composants sur la même face. Ça simplifie la lisibilité pendant le routage et pendant le montage de la carte. Mettre des composants sur les deux faces peut faire gagner en surface, mais il y a moins de place pour les vias, donc le gain n'est pas doublé.

- Si on a des composants traversants, on peut faire passer des pistes dessous. Pour pouvoir en tirer parti il vaut mieux aligner les composants, plutôt que de les mettre dans des sens différents. Par exemple, si on a beaucoup de résistances, il vaut mieux les mettre toutes parallèles les unes aux autres. Ca permet d'optimiser le placement, et ça facilite le routage en X-Y (voir plus bas).

- Les capas bypass / tank des circuits intégrés doivent être placées au plus près des pins d'alim des composants en question.

1) Placer les connecteurs, généralement plutôt en bord de carte, et vers les faisceaux auxquels ils doivent se relier.

1b) Si il y a des zones isolées électriquement, c'est le moment de les définir. En effet, d'une part il faudra que ces zones soient monolithiques, mutuellement exculsives et le plus convexes possibles (pas de frontières biscornues entre les deux). D'autre part, si il y a isolation électrique, il faudra garantir une zone sans cuivre entre les zones, zone qui devra avoir une largeur minimum garantie tout au long de la frontière. Donc plus la frontière a une forme compliquée, plus il va être difficile de garantir cette isolation sans se prendre la tête, géométriquement parlant.

2) Composants de puissance : proches des connecteurs où sort la puissance, si possible dans une zone "proche du bord".

3) Les "gros composants", mais pas de puissance, ce sont ceux qui ont beaucoup de pattes (MCU, FPGA, SBC, modules ...). En général on cherche à placer ces composants proches le centre de la carte. D'autant plus s'il n'y en a qu'un seul (genre un MCU). Le mieux est d'excentrer dans le sens des connections : plus il y a de connections vers un connecteur, plus il faut le rapprocher de ce connecteur. Ça permet de faciliter le routage, et en plus ça permet de choisir comment placer plusieurs gros composants.

Un truc qui marche pas mal, c'est de placer les composants sur une sorte de barycentre entre les connections avec l'extérieur de la carte. <A compléter> En gros, il faut regrouper les composants par fonction, et rapprocher chaque fonction des connecteurs vers lesquelles elles vont. Approximativement pour le moment, le but est juste de voir vers où vont les signaux connectés au gros composant. Ensuite, voir de quel côté il y a le plus de signaux qui vont vers le gros composants. C'est vers ce coin-là qu'il est préférable de poser le gros composant. Pas collé au connecteur vers lequel il a le plus de connexions, mais s'en rapprocher. Ca peut paraitre contre-intuitif, car on pourrait s'imaginer que ça créée de la congestion. En pratique ça facilite le routage, car il y aura moins de longues pistes à tirer.

4) S'il y a des signaux rapides / différentiels, placer les composants concernés le plus proche possible des connecteurs concernés, pour que les pistes soient le plus directes vers la sortie.

5) Placer le reste, normalement ça n'est pas trop dur, il n'y a plus que des petits composants.

Pour faire une analogie, l'idée c'est que quand on doit faire rentrer des gros cailloux et du sable dans un bocal, il vaut mieux d'abord mettre les cailloux, parce que le sable va pouvoir s'infiltrer facilement entre les cailloux. Par contre l'inverse marche moins bien. Les gros cailloux ce sont les gros composants (connecteurs, composants de puissance, composants avec beaucoup de pattes), le sable c'est le reste.

Une fois que les composants sont placés, on peut commencer à tirer les pistes. Concernant le routage automatique : ce n'est pas conseillé. Même après un bon placement le routage automatique va donner des résultats aléatoires, et il est plus intéressant de passer un peu de temps à tirer des pistes que de se fier à un algo qui souvent n'est pas efficace.

Routage

Tirer les pistes est un mélange entre du dessin et de la résolution de puzzle. C'est très long et pénible, et parfois hypnotique (sur mon premier routage au taf, je ramais tellement que j'en rêvais la nuit).

Pour tirer les pistes, on sélectionne le mode "track", on clique sur un pad, et on dessine la piste jusqu'à son arrivée. L'on remarquera que, lorsque l'on cherche à faire un trait qui n'est pas à 90°, la piste dessinée est automatiquement contrainte, par défaut / en général avec des angles à 45°. On peut configurer pour avoir des angles à 90° (déconseillé) ou des arrondis à 90° ou 45° (ok). Lorsqu'on clique, on "fixe" / "commit" la piste telle qu'affichée, depuis le départ jusqu'à la première jonction (premier angle), ou au dernier angle avant la position de la souris (dépend du logiciel, de la configuration ...). Chaque clic fixe jusqu'à l'angle suivant. Arrivé à la fin, le clic "finit" la piste, qui alors ne suit plus l'outil. Pendant tout le temps que l'on tire la piste, le chevelu de la piste suit la fin de la piste affichée, et continue d'aller jusqu'à la destination de la piste, ce qui permet d'avoir une idée de là où il faut aller.

Pour ajouter un via et changer de couche, il suffit, alors qu'on est en train de tracer une piste, de changer de sélectionner la couche où l'on veut aller, le via sera ajouté automatiquement.

On peut également dessiner des formes - généralement des polygones mais certains outils de CAO permettent plus de fantaisie - qui seront remplies de cuivre ou détourée de cuivre. On appelle une zone de ce type un "plan", ou un polygone. S'il est rempli de cuivre, on parle de plan de cuivre, ou "polygon pour" (in english). Les plans sont pratiques pour remplir rapidement de grandes surfaces, ce qui permet de baisser les impédances et de passer plus de courant.

La largeur d'une piste définit sa résistance linéique, et son échauffement. Plus une piste est fine, plus elle chauffe vite et fort quand on y fait passer du courant. Cet échauffement provoque une montée en température du cuivre et du substrat, ce qui peut conduire à une destruction de la piste (le cuivre brûle), une délamination du substrat, voire un départ de feu. Pour éviter cela, il faut dimensionner la largeur des pistes par rapport au courant qu'elles vont voir passer. Plus le courant est élevé, plus la largeur de piste doit être grande. La relation est définie par rapport à l'échauffement maximal toléré sur les pistes par rapport à la température ambiante avant d'atteindre les températures de délamination / passage à l'état visqueux du substrat (température toujours plus faible que la fusion du cuivre). En général on utilise des abaques ou des applets de calcul automatisé (il y a un outil pour ça dans Kicad), genre [1] [2] [3] [4]. Connaissant la largeur voulue, on dit au logiciel de CAO quelle largeur on veut et il dessinera la piste avec cette largeur. Vu que les pistes sont généralement dessinées sous forme d'assemblage de cylindres, le résultat peut être peu esthétique, on pourra alors le dessiner sous forme de polygone.

Étant donné que router des pistes larges est vite très compliqué - car elles prennent beaucoup de place et gênent le reste du routage - il faut autant que possible ne faire des pistes larges que lorsque strictement nécessaire. Toutes les pistes de signal avec un courant faible doivent être routées avec une largeur faible pour faciliter le routage.

La classe choisie pour le routage donne la largeur minimale d'une piste. On peut prendre cette largeur par défaut pour toutes les pistes, et n'agrandir que celles qui passent du courant. Exemple en classe 4 : 0.2mm de largeur de piste et 0.2mm d'isolation, donc on route tout en 0.2mm, et on calcule la largeur uniquement lorsqu'il y a du courant. Si on a aps de contrainte de place, on peut router avec des pistes plus larges que la classe atteignable, de façon à faciliter la fabrication. Sur le process du lab, 0.5mm de largeur est une assurance de réussite de gravure, 0.25mm nécessite un peu d'attention pour ne pas graver trop.

Les paramètres de routage Largeur des pistes, isolation, via to via, via to pad, track to pad, track to pad, etc.

Ordre conseillé pour le routage après placement

- Puissance

- Signaux rapides / différentiels

- Le reste

- Alims faible courant

- Masses / plans de masse

Lorsque l'on routage sur plusieurs couches, une méthode très efficace est le routage X-Y. Cette méthode consiste à choisir un sens différent (vertical, horizontal) pour la "direction générale" des pistes pour chaque couche, et tâcher de se tenir à ce sens de routage, même s'il est possible de passer "tout droit" sur une seule couche. Sur deux couches, on aura donc une couche sur laquelle on route horizontalement, et une couche sur laquelle on route verticalement.

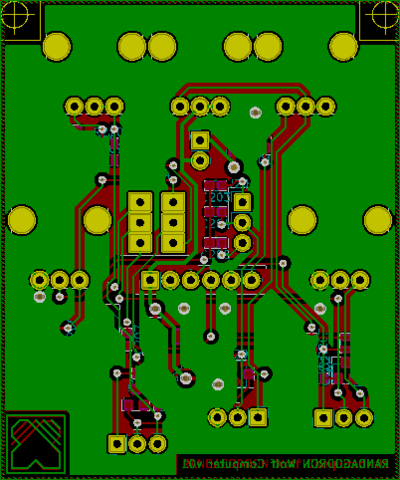

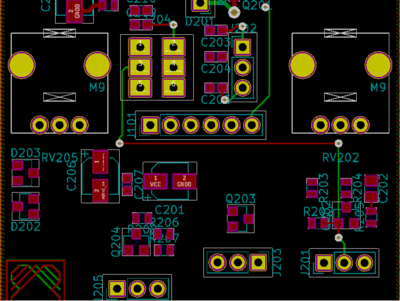

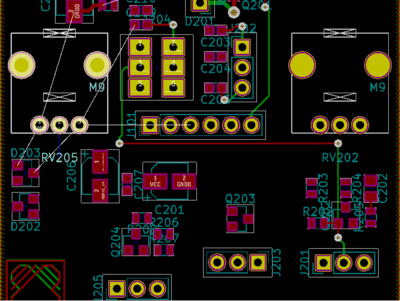

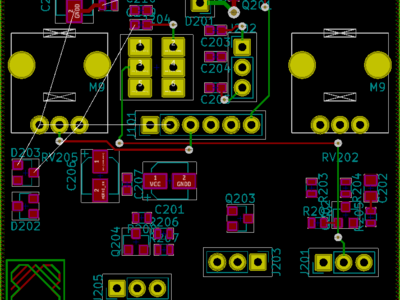

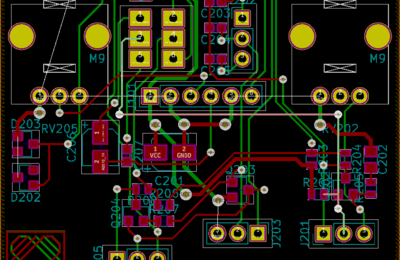

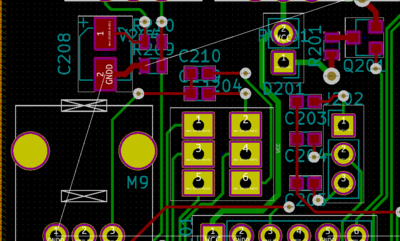

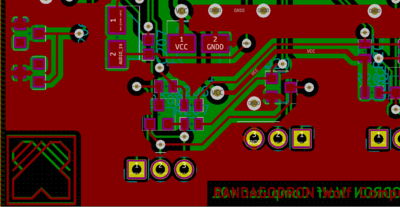

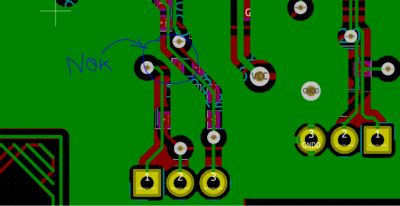

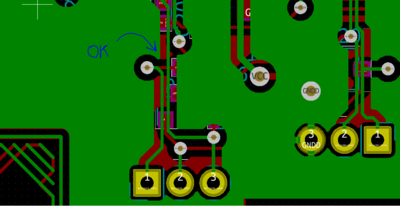

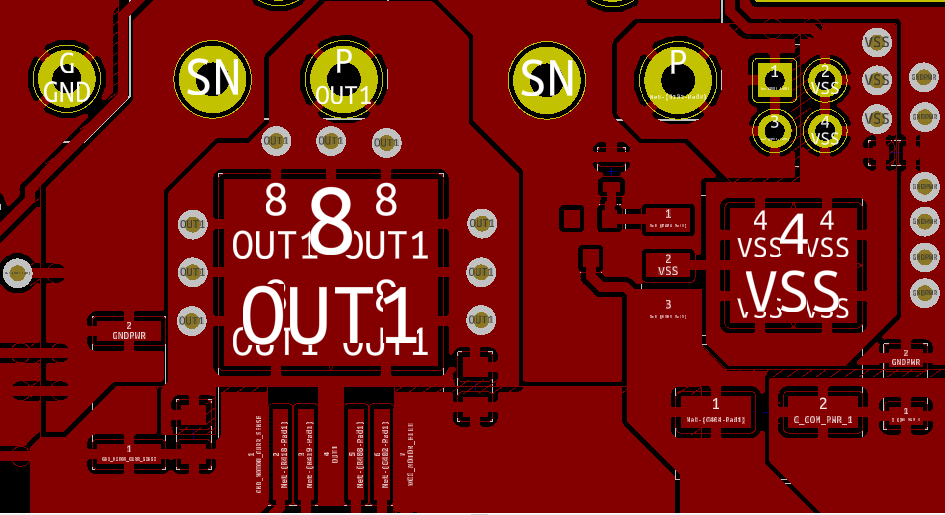

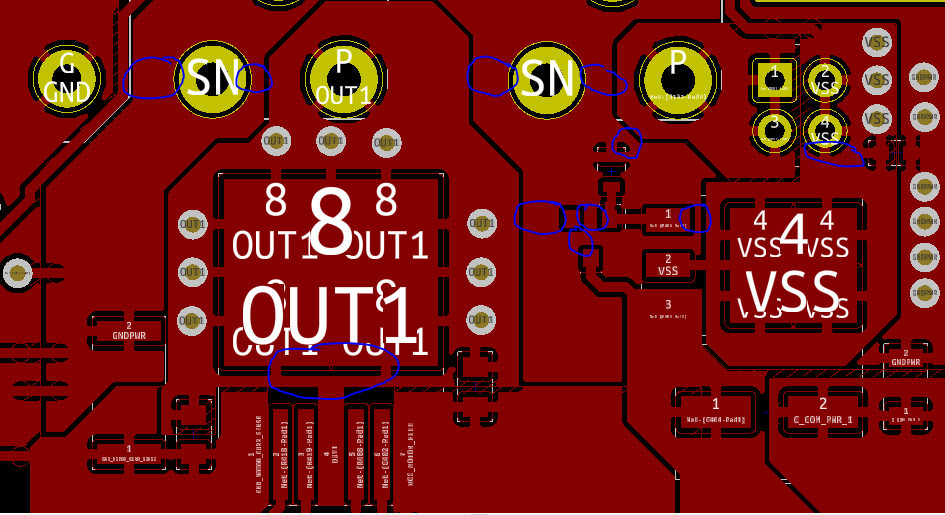

Exemple sur une carte de mon crû, les piste sur le top (rouge) sont routées horizontalement, les pistes sur le bottom (vert) sont routées verticalement:

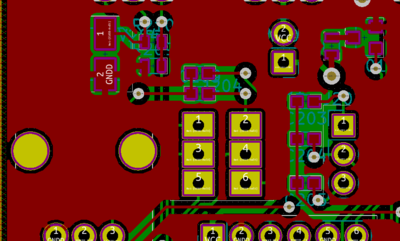

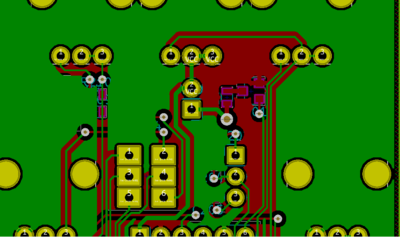

On voit mieux sans les plans de masse:

L'on remarque que les pistes ne sont pas toutes strictement horizontales ou verticales sur une couche. Néanmoins, le "sens général" des pistes est horizontal sur le top, vertical sur le bottom. L'idée est, pour relier deux composants qui sont éloignés l'un de l'autre, et pas au même niveau horizontal et/ou vertical, de se forcer à passer par la couche top quand on doit se déplacer horizontalement, et par la couche bottom quand on doit se déplacer verticalement. Si on a, par exemple, deux composants CMS sur une même face, un en haut à gauche du PCB, l'autre en bas à droite, pour tirer une piste entre les deux, plutôt que de tirer une piste en direct à 45° sur leur face, il vaut mieux tirer deux pistes horizontale qui se rejoignent au même niveau horizontal, puis passer sur la couche bottom pour les relier en hauteur.

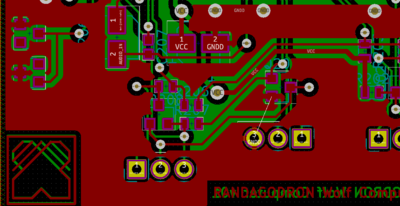

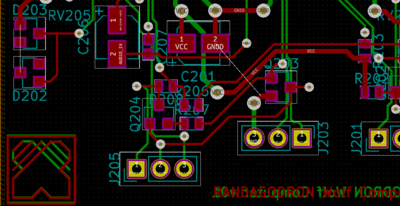

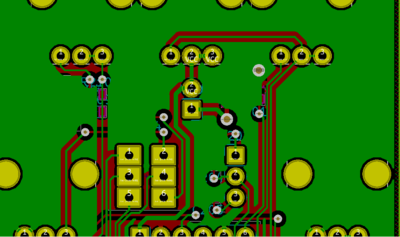

Exemple sur une piste en particulier:

Ici la piste pourrait être tirée entièrement sur le bottom et en direct, mais on préfère passer par le top pour se déplacer horizontalement, et sur le bottom pour se déplacer verticalement. Ce la permet de garder le passage pour les futures autres pistes qui pourraient la croiser. Par exemple, pour passer la piste suivante, entre la pin 2 de RV205 et la pin 3 de J101:

Je fais de même, ce qui m'évite tout croisement:

Ceci permet d'aboutir quand de nombreux signaux se croisent, comme ici:

Le placement des composants peut guider le choix de quelle couche est dans quel sens. Par exemple, si on a des circuit intégrés en boîtiers DIP / DIL / SOIC etc. (à deux rangées de pattes), il est préférable de les orientés tous dans le même sens, de façon à avoir toutes les pattes qui "sortent" dans le même sens (horizontal ou vertical) et donc de router sur la face de connexion des pistes dans le sens de sortie des pistes. Plusieurs cas se présentent:

- Circuits intégrés CMS sur une seule face : les pistes sortent sur la face où sont posés les composants. Cas le plus simple.

- Circuits intégrés CMS sur les deux faces : les composants seront placés orthogonalement entre les deux faces, dans le sens de routage choisi.

- Circuits intégrés traversants, vias traversants : la connexion aux pistes se fait sur la face opposée aux composants, donc on route sur la face opposée, et on "sort" du composant dans le sens de sortie des pattes du composants.

- Circuits intégrés traversants, vias métallisés : La connexion aux pistes se fait sur n'importe laquelle des deux faces, on route toujours dans le sens de sortie des pattes du composant.

- Mix composants CMS + composants traversants, composants sur une seule face, vias traversants : mettre les CMS orthogonaux aux traversants, pour que toutes les pistes arrivent dans le bon sens sur tous les composants.

- Mix composants CMS + composants traversants, composants sur les deux faces, vias traversants : idem précédent, mais les CMS sur les deux faces n'auront pas la même orientation.

- Mix composants CMS + composants traversants, composants sur les deux faces, vias métallisés : idem précédent, mais on peut choisir sur quel côté les CMS sont orthogonaux aux traversants.

<Mettre des photos / schémas !!>

A NOTER : il n'est pas obligatoire de suivre ces règles / proposition de configuration, il peut même y avoir des cas où il n'est pas possible de les suivre. Néanmoins, suivre ces règles dès le placement permet de se faciliter la vie, et rend le routage moins difficile et moins long.

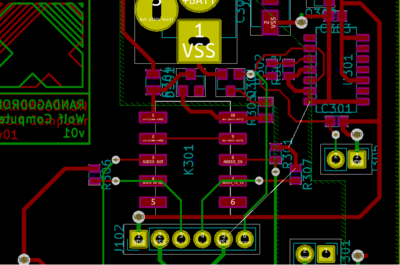

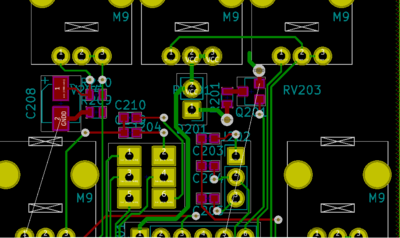

Par exemple, ici j'ai un relai en DIL CMS, posé sur le top, donc je route horizontalement sur le top, et j'utilise le bottom pour router verticalement:

L'on est pas obligé de faire horizontal / vertical, ce qui compte est d'avoir deux sens orthogonaux. On peut donc faire des pistes en diagonale, et croiser entre deux couches, ça fonctionne, personnellement je trouve ça moins pratique, mais ça peut être plus joli, ou faciliter le routage dans certains cas.

Sur des routages à plus que deux couches avec des signaux, il est conseillé de continuer à router en X-Y par paire de couches, mais il n'y a pas vraiment de règle générale, tout dépend du contexte.

Ordre de routage <A remettre d'équerre avec les autres parties !!>

- Lignes de puissance (pistes larges, polygones), faire au plus court, router les masses de puissance avec, et coller ces pistes les unes aux autres le plus possible (les coller à la masse de puissance surtout). Éviter de changer de couche, mais si vous y êtes forcé ne pas oublier de mettre suffisamment de vias pour passer le courant. Ne pas oublier que le courant qui rentre par la piste d'alim doit sortir par la piste / plan de masse. Donc prévoir la bonne largeur pour l'alim ET la masse de puissance, et les équilibrer. Idem pour les vias : si on doit faire des vias sur une piste de puissance et la masse associée, mettre le même nombre de vias sur la piste d'alim et sur la piste de masse.

- Signaux rapides et différentiels, faire court et direct, éviter de changer de couche autant que possible.

- Le reste

- Alims sans courant (AOP, capteurs), partir de l'alim, aller aux capas bypass / tank, puis aux pins des composants.

- Optimiser les vias si routage en X-Y (supprimer les sauts de couche inutiles)

- Tracer les plans de masse et générer pour voir ce que ça donne

- Rapprocher les pistes pour agrandir les plans de masse : plus il y en a mieux c'est. S'il y a des signaux sensibles (haute fréquence, très basse impédance), ne pas les coller à d'autres signaux, mais plutôt laisser un peu de plan de masse autour pour les isoler. <photo>

- Reconnecter les plans de masses non reliés en ajoutant des pistes de masse et des vias

- Ajouter les mires / fiducials / textes

On dit traditionnellement qu'on "ne route pas les masses". L'idée derrière cette expression est que les connexion des composants à la masse se feront par un plan de masse qu'on génère une fois que tous les signaux autres que la masse ont été tirés. Dans un routage idéal (comprendre : qui se passe idéalement bien), une fois que l'on a fini de tirer les signaux, on génère le polygone de masse et toutes les masses sont reliées entre elles.

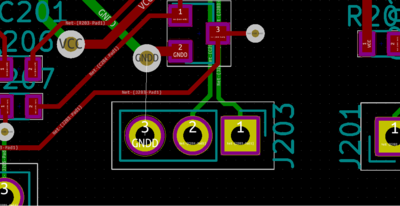

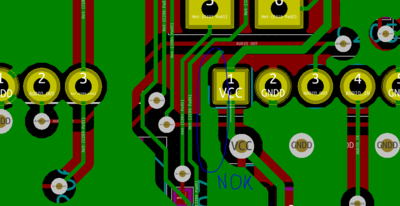

Exemple, ici, pas la peine de relier la pin 3 de J203 à la masse par une piste :

Une fois que l'on a tiré toutes les autres pistes, et que l'on a fait le polygone de masse sur l'intégralité de la carte, on génère le polygone et la jonction à la masse se fera automatiquement:

Si une piste a été tirée malgré tout, ce n'est pas très grave, elle sera noyée dans le polygone de masse.

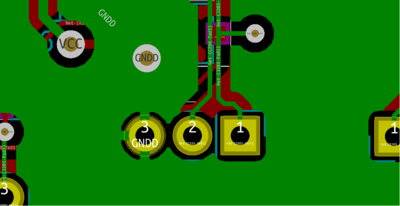

Autre exemple, ici on ne connecte pas la masse de C208 et R209 avec les autres masses:

Pas besoin, car une fois les polygones générés, le plan de masse relier tout cela dans la joie et la bonne humeur:

Je précise "dans un routage idéal" car il peut arriver que de connections ne se passent pas, s'il y a trop de pistes qui se croisent, et si des vias ou des découpes dans le PCB créent des points de congestion. Par exemple ici:

L'on voit que la masse de Q203 n'est pas reliée, il y a un petit îlot de masse autour de la pin, mais elle n'est pas reliée aux autres masses. Donc, dans ce cas, il faut ajouter une piste et un via, de façon à relier:

Et, maintenant, quand on génère les polygones, la connexion est présente, la piste est noyée dans le plan de masse, et le via permet de connecter l'îlot de masse au reste du plan:

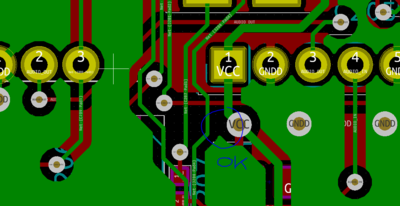

Il peut rester des îlots non connectés à la masse, mais qui n'ont pas de composants connectés à la masse, par exemple ici:

Ici on a une zone entourée de pistes qui ne sont pas reliés à la masse, avec aucune pin de composant reliée à la masse à l'intérieur. Fonctionnellement, ce genre d'îlot n'est pas gênant, car il n'y a pas de net non-connecté ici. Par contre, c'est assez disgracieux, et si on grave le PCB à la main / en DIY, on va consommer du perchlo pour rien à creuser ce trou. On peut donc le remplir, de la même façon que précédemment, en ajoutant une piste et un via. Ici on va se connecter au SOT-23 qui est sur le top de l'autre côté:

Et on re-génère les polygones:

Remplir tous les îlots n'est pas forcément une bonne idée, car cela ne permet pas de diminuer l'impédance de la masse (aucun courant ne va passer par cette zone), et cela augmente la surface du plan de masse, ce qui peut le rendre sensible aux émissions électromagnétiques, et donc générer du bruit. Tout dépend de l'usage, et du niveau de manie de la personne réalisant le routage. ici, c'est de l'audio pour guitare, donc bande passante assez faible, et c'est moi qui route, donc niveau de manie élevé, d'où : on remplit tous les îlots.

Lorsque l'on génère les polygones des plans de masse, il est toujours préférable d'éviter d'avoir des goulots d'étranglement - qui limitent le courant qui peut passer et donc modifient l'impédance de la masse. Exemple:

Ici, soit on agrandit le "canal" de passage vers l'îlot, soit on ajoute un via, soit on modifie les pistes alentours pour qu'il n'y ait pas d'îlot. Si on choisit de ne plus avoir l'îlot, ça donne ceci:

Autre chose à éviter : de longues et fines sections de cuivre - qui font de très bonnes antennes. Exemple:

Dans ce cas, il vaut mieux modifier les pistes alentours pour ne pas avoir d'îlot en longueur. C'est relativement disgracieux, mais ça élimine l'antenne:

- Pour "résoudre le puzzle", il faut arriver à relier tous les fils du chevelu en faisant les chemins les plus courts.

- Sur du routage simple face, en cas de blocage (deux pistes qui se croisent sans possibilité de contourner), on peut utiliser un strap. Il s'agit d'un fil qui va être monté comme une résistance traversante, pour passer par-dessus une piste. En multi-couche, on change de face. Si on utilise des composants CMS, il est très difficile de ne pas avoir des straps ou de ne pas changer de face.

- Un jeu Android est pas mal pour se rendre compte des contraintes de routage en simple face - et s'entrainer à les résoudre : Flow Free

- Virages sur les pistes : Toujours tourner à 45°. Idéalement faire des arcs de cercle.

- La largeur de pistes définit le courant max qu'on peut passer dans une piste -> plus c'est large, plus ça passe de courant. Le mieux c'est de définir des classes de nets, avec les largeurs associées, pour que le logiciel adapter automatiquement la largeur quand on tire la piste.

- On ne route pas les masses (voir les dernières étapes), sauf les masses de puissance s'il y en a, pour garantir qu'elles pourront faire passer le courant de puissance.

- En double face, router de préférence en X-Y (voir plus haut).

- En simple face + composants traversants, on peut faire du simili X-Y si les composants sont mis tous dans le même sens : router préférentiellement des pistes qui vont perpendiculairement aux composants traversants.

- Quand on fait partir une piste d'un pad traversant, bien réfléchir au côté sur quelle face du PCB on pourra souder. Attention aux connecteurs HE10 genre ceux des Arduino : on ne peut pas souder sur la face contre laquelle la carte est posée ! Il est facile de se faire avoir sur ce point car le logiciel de CAO considère que les vias et trous sont métallisés, et donc que la connexion électrique sur les trous est automatique entre les deux faces.

Si on prend l'exemple d'une vulgaire barrette HE10, posée face top, les pins vont ressortir sur le bottom. Côté bottom on verra donc:

Comme on peut le voir, là où il y a une flèche, on peut mettre un coup de fer à souder. Par contre, côté top ...

... hé bien on ne pass pas le fer à souder. Donc si il y a une piste qui se connecte à un pad de ce connecteur sur le top, on ne pourra pas la connecter électriquement. Fail ... Donc il faut que la piste parte du pad sur le bottom.

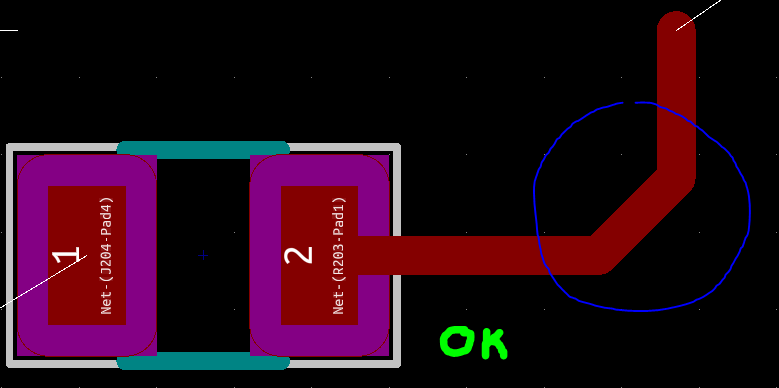

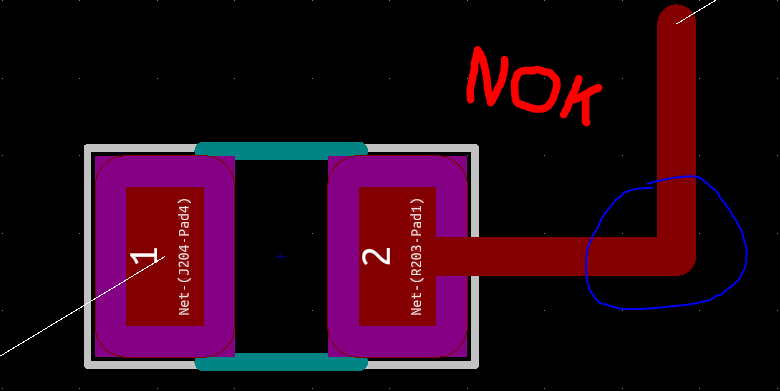

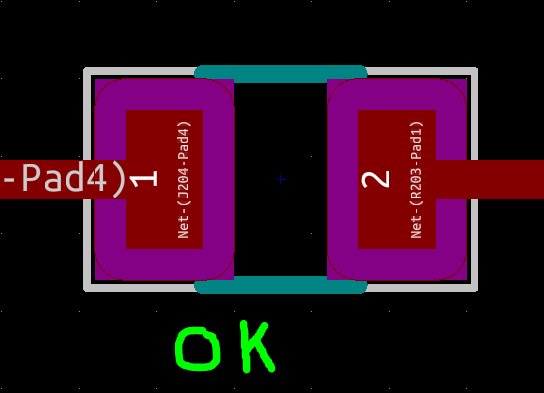

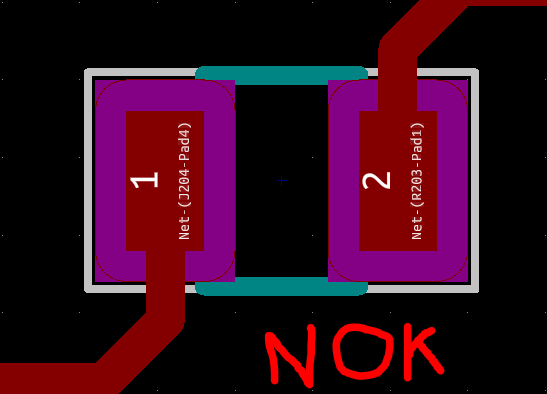

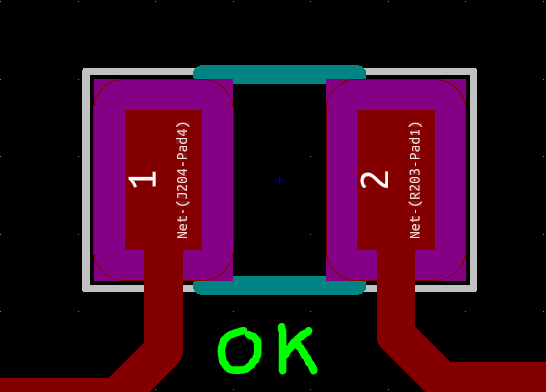

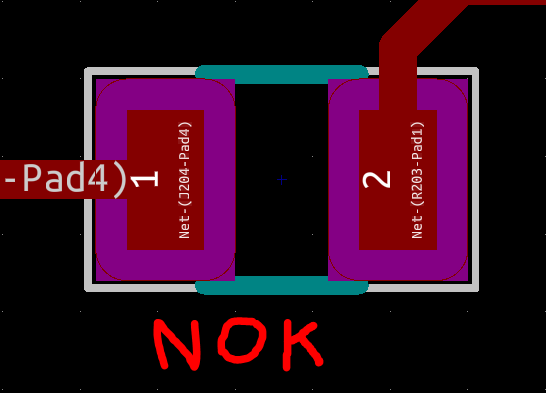

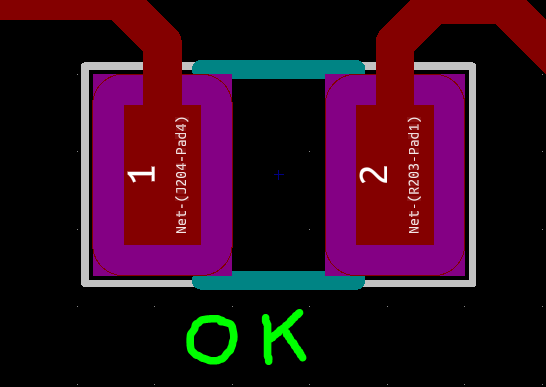

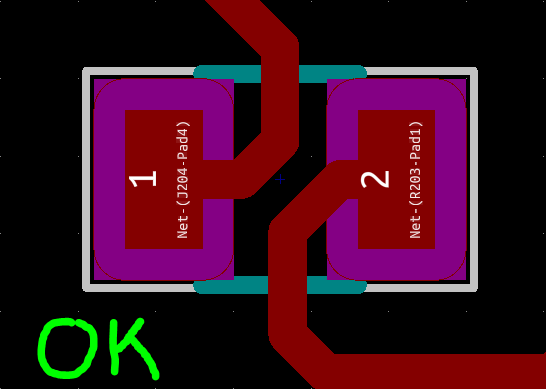

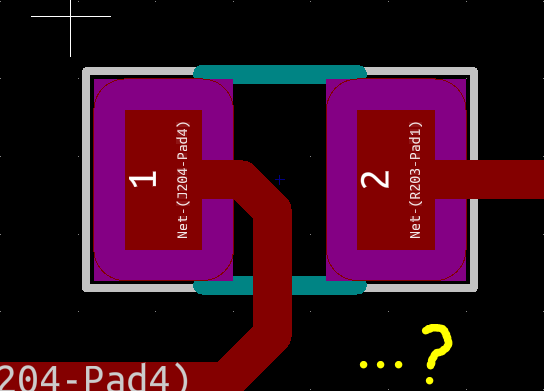

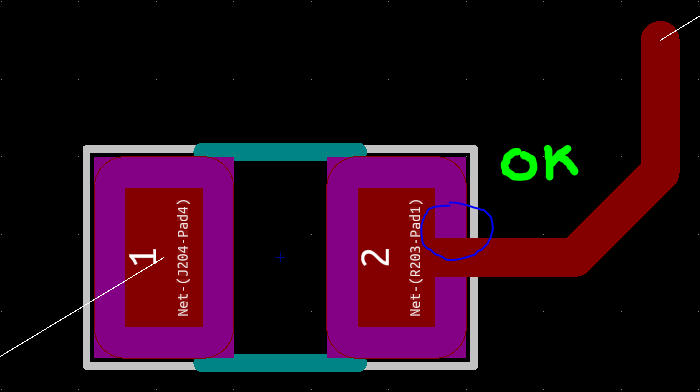

- Quand on fait partir une piste d'un pad CMS, sur un composant passif en petit boîtier genre 0603 et en-dessous, il est préférable que les piste sur chaque pad partent dans la même direction. Cette règle est applicable surtout pour les cartes qui sont fabriquées à la refusion, car elle permet d'éviter l'effet "tombstone", ou "effet Manhattan", qui fait que ces petits composants se "lèvent" à la refusion du fait d'un refroidissement non-homogène et non-symétrique de la patte à braser. Si vous soudez à la main -> inutile.

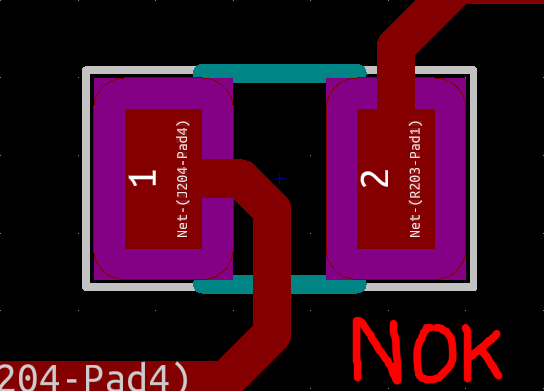

J'ai un doute sur le dernier, dans le doute il faut partir du principe que ça n'est pas bon.

- Si la carte est montée industriellement avec refusion + vague pour les pads traversants, prévoir un espace sans composants et sans vias sur le bottom (côté soudure) autour des pads traversants. Ceci pour permettre à la buse de soudure à la vague de passer sans "noyer" des composants.

- Éviter les angles aigus. Ca se grave mal, quel que soit le process.

- Si vous fabriquez vous-même, évitez de faire des pistes trop fines. 0.5mm ça reste vérifiable visuellement, en-dessous c'est chaud. S'il y a besoin de serrer des pistes, il vaut mieux n'avoir que les pistes concernées qui soient plus fines, et garder les autres à une largeur plus élevée, voir ne réduire la largeur de piste que localement.

- Prévoyez de l'espace pour mettre du texte (nom de la carte, révision du routage), que cela soit dans le cuivre ou bien un espace vide pour coller une étiquette (à prendre en compte pour le calcul du ratio de surface).

Lorsque l'on doit faire des pistes de puissance (=qui vont passer un courant conséquent), les pistes devront avoir une largeur importante, et il est pertinent de se poser la question de la façon de dessiner ces pistes. Deux options:

- Dessiner des pistes "classiques", avec une largeur plus élevée : le logiciel de CAO va garantir que la piste fait en tout point de sa longueur la largeur suffisante pour passer le courant, il n'y aura pas de point de congestion. Par contre, la forme de la piste restera une grosse ligne à bouts arrondis, ce qui peux gêner le routage.

- Dessiner un polygone : on peut faire une forme très précise qui va épouser le bord de carte, les bords des composants de puissance, etc. Par contre, il faudra vérifier "à la main" qu'il n'y a pas de point où la largeur de la piste est insuffisante pour passer le courant requis, ce qui deviendra un point de congestion. (A noter que certains logiciels de CAO doivent disposer d'outils permettant de vérifier ce point automatiquement, que je sache Kicad ne le fait pas).

Donc, faire des polygones pour les pistes de puissance permet d'optimiser l'utilisation de la surface, mais créé plus facilement des points de congestion.

Voici un exemple de pistes de puissance routées avec des polygones:

J'arrive à utiliser l'intégralité de la surface disponible pour y mettre du cuivre. Par contre, il y a sur cette face plein de points de congestion, et il faut vérifier qu'aucun ne limite tellement le courant qu'il empêche le circuit de fonctionner correctement:

Tout cela doit être géré.

Dissipation thermique dans le PCB

Si le circuit comporte des composants qui dissipent beaucoup de puissance, il faut dissiper cette puissance en-dehors du boîtier du composant.

Pour déterminer si un composant entre dans cette catégorie, je renvoie aux méthode de design thermique, puissance dissipée dans les composants, etc. Pour résumer et donner un ordre de grandeur, si un composant dissipe suffisamment de puissance pour faire monter la température de son boîtier au-delà de l'operating max temperature, il faut dissiper la puissance dans le PCB, sinon le composant va tomber en rade en fonctionnement, voire se détruire s'il n'a pas de protection.

Pour que cette dissipation soit possible, il faut faire une connexion thermique entre le boîtier et le PCB. Deux solutions :

- Par "contact sec" : dissipateur + vis + graisse thermique, permet de dissiper de grosses puissances, mais prend énormément de place, et est peu fiable, sensible au vieillissement de la pâte thermique, aux vibrations ...

- Par dissipation directe dans le PCB, ce dont je parle ici, permet de dissiper moins de puissance qu'un dissipateur externe, mais est infiniment plus fiable.

Certains boîtiers sont plus propices à la conduction thermique que d'autres, raison pour laquelle les composants de puissance sont fabriqués dans ces boîtiers : TO-220, DPAK, D²PAK, SOT-223, etc. Ces boîtier disposent d'une grande surface de contact pour la soudure sur un (ou plusieurs) de leurs pads, ce qui permet un meilleur transfert thermique de la puissance dissipée du composant à travers le boîtier et à travers le PCB. Corollaire : ces pads sont difficiles à souder, il faut donc faire attention au routage et à la fabrication / soudure.

Pour faciliter la soudure, un utilise souvent sur les empreintes des freins thermiques, qui permettent de limiter la dissipation thermique instantanée, tout en gardant un bonne dissipation thermique moyenne. Exemple ici, il s'agit d'un boîtier D²PAK dont le pourtour est "découpé" dans le plan au lieu d'être fondu / noyé dans le plan. Ce découpage est le frein thermique:

A noter que l'ajout de vias permet d'augmenter à la fois la masse de métal contenue dans le PCB, et améliore également légèrement la convection, donc améliore la dissipation thermique. Et, corollaire logique, ces vias peuvent aussi rendre la soudure encore plus difficile, logique.

A lire à ce sujet: Chez Infineon, Resistance - Theory and Practice

Chez Würth, management of circuit boards

Chez Cree, un exemple d'application sur une LED de puissance CMS, PCB Thermal Performance for Cree® XLamp® LEDs

Chez TI, Thermal Design By Insight, Not Hindsight, and IC Package Thermal Metrics

Chez IRF (racheté par Infineon), [5] Application Note AN-1057 Heatsink Characteristics

Ce qui est à retenir : dissiper dans le PCB signifie augmenter "artificiellement" la surface de dissipation des pads de dissipation des boîtiers, en y connectant les pistes / plans de cuivre du PCB qui font office de dissipateur additionnel. La conduction thermique entre le boîtier et le cuivre du PCB se fait par la brasure. Cette augmentation a des limites : la chaleur ne se répands pas uniformément dans le cuivre, et au-delà d'une certaine surface de cuivre additionnel, le gain en résistance thermique devient négligeable (voir le doc Infineon à ce sujet, hautement intéressant). Il y a donc une surface optimale. Par ailleurs, le fait d'ajouter des couches reliées par des vias permet d'ajouter de la masse de cuivre pour la dissipation, mais avec les inconvénient suivants:

- Les couches internes (si on les utilise) peuvent difficilement évacuer la chaleur par convection (vu qu'elles sont emprisonnées à l'intérieur du PCB) et ont donc une moins bonne dissipation que les deux couches externes (qui peuvent dissiper librement en convection, étant directement en contact avec l'air).

- Si l'on utilise des vias, on gagne légèrement de convection, mais la conduction thermique entre les couches sera forcément moins bonne qu'une liaison directe telle sur sur la couche sur laquelle le composant est soudé, ce qui limite là aussi le gain en dissipation.

Par contre, si on fait une jonction thermique avec la face opposée au composant, on peut créer un contact avec un dissipateur en le posant simplement contre le PCB. C'est ce qui se fait dans les calculateurs automobiles : la dissipation se fait à travers le boîtier en tôle ou en alu, qui sert de masse de dissipation thermique, contre lequel est posé le PCB, avec un produit de contact, généralement un film isolant électrique - mais conducteur thermique - type gap-filler.

Cette solution est loin d'être miraculeuse. Mais elle a l'avantage de ne pas requérir de composants supplémentaires (dissipateur passif, actif ...) et de ne consommer "que" de la surface de cuivre.

Vias traversants / non-traversants / bouchés / pas-bouchés

Si vous fabriquez vos PCBs vous-même, il est fort probable que vous ne puissiez pas faire de vias métallisés. Dans ce cs les connexions entre les deux couches - car vous serez limité au PCB double-face - se feront en mettant un bout de fil dans le via, qui sera soudé de chaque côté. Il va de soi qu'il ne faut pas qu'il y ait de composant sur le via, sinon on ne peut pas souder le composant, vu qu'on ne peut pas le poser à plat sur le PCB, vu qu'il y a un via traversant qui dépasse.

Si vous avez un process de trous métallisés - DIY ou industriel si vous faites fabriquer - alors vous pouvez mettre des composants sur les vias, ces derniers étant affleurants, on peut poser les composants à plat, et donc souder.

Les vias métallisés peuvent être bouchés ou non, et bouchés par l'étain ou par le vernis (s'il y en a). Tout dépend du diamètre du via et du process de soudure. Certains process permettent de mettre de la brasure sur les vias pour qu'à la refusion ils se bouchent. Certains process permettent de ne pas mettre de vernis sur les vias, pour pouvoir y avoir accès pour test, ou bien au contraire recouvrent les vias de vernis, de façon à éviter l'oxydation.

Points particuliers

Vias traversants On ne peut pas en mettre sous les composants, attention.

Vias Attention, ils ne peuvent pas passer un courant infini. Sur une piste de puissance, si on change de couche il faut mettre plusieurs vias pour passer le courant (ou un vias beaucoup plus gros). D'une façon générale il faut éviter de faire des sauts de face sur les signaux de puissance. Pareil sur les signaux haute-fréquence : limiter les sauts de face.

Oscillateurs / horloges MCU et cie Faire le plus court et le moins de surface possible, isoler la masse locale <photo>

DCDC / alims à découpage La boucle du découpage doit faire la plus petite surface possible <photos>

Capas bypass / découplage des circuits intégré Au plus près de la pin d'alim positive, sur le chemin de la piste <photo>

[[Circuits de protection ESD] Au plus près du connecteur, sur le chemin du courant <photo>

HT (haute tension) Isolation 4mm pour le 220V, l'air est plus conducteur que le substrat FR4 <voir refs url>

Capas céramique CMS sur une alim non limitée en courant En mettre 2 en série, placées à 90°. Pas de capa tantale sur une alim non limitée en courant (batterie). <photo>

D'une façon générale, les capas céramique sont des composants fragiles, sensibles à la flexion du PCB. Il faut faire attention à leur placement, et ne pas les mettre dans une zone qui risque de subir des déformations. Le plus souvent ça peut avoir lieu utour des trous de fixation par vis : quand on vis, on va contraindre le PCB qui va se déformer localement. Donc éviter de mettre des capas céramique proche des trous de fixation par vis. Idem si il y a des connecteurs montés à force (press-fit), il va y avoir des micro-vibrations locales au moment du montage du connecteur, et des capas montées proches pourraient casser. Les écarter.

Capas chimiques + composants qui chauffent Pas bueno ! (Écarter les capas électrolythiques des composants ou pièces mécaniques qui chauffent, pour améliorer leur durée de vie. Pour info, la durée de vie donnée par les constructeurs est données pour un fonctionnement à la température max nominale (ex.: 85°C / 1500h c'est garanti 1500h à 85°C permanent de température de la capa, ambiant + auto-échauffement). La durée de vie double tous les 10°C en-dessous de la température max du composant. Ce qui signifie qu'une capa spécifiée 85°C / 1500h dure 3000h à 75°C, 6000h à 65°C, 12000h à 55°C, etc. Donc ça vaut le coup de leur éviter un coup de chaud !

PCB avec plus que 2 couches Prévoir une couche dédiée au plan de masse et une couche dédiée aux plans d'alims. Aucune piste sur la couche de plan de masse. on peut passer quelques signaux sur la piste de plan d'alim (sans abuser). Mettre la couche de plan de masse en couche interne la plus proche de la face qui a des composants (si composants sur les deux faces -> plus proche de la face qui a les gros composants / composants de puissance, ou le plus de composants). Ce qui donnera:

| Top (signaux) |

| Power in (masse, alims) |

| Signal in (signaux) |

| Bottom (signaux) |

Au-delà, on ajoute des couches de signaux en interne. On peut avoir une couche dédiée alims et une couche dédiée masses, voire même plusieurs pour chaque ! <mettre des exemples de stackup en > 4 couches>

Mires Les mires ont pour but de permettre aux outils de fabrication de s'aligner correctement, ce sont des repères visuels. Dans l'industrie elles serent surtout pour les outils de test fin de chaîne et - surtout - au pick 'n' place. Elles doivent être présentes sur les couches cuivre, sur les deux faces, et dans la surface de la carte. Si le montage des composants se fait sur le panneau, on peut aussi mettre des mires sur les marges du panneau. Normalement deux suffisent à deux extrémités de la carte (le plus éloignées possible), mais il peut être préférable (voir requis par le câbleur) d'avoir des mires proches des composants avec un pitch un peu fin (VQFP, BGA ...).

Sur un process manuel elles permettent surtout d'aligner les couches pendant la fabrication du PCB (aligner les typons pour l'insolation). Dans ce cas pas obligé de les mettre dans la carte, on peut les mettre en dehors, tant qu'on imprime le typon plus large que la surface de la carte, pour pouvoir aligner manuellement.

<Exemples de mires>

Panneaux

Considérations pécuniaires

on dépasse un peu du strict cadre du routage, mais quelques infos pour économiser des $$$. Si vous faites fabriquer votre PCB, il y a certains points à prendre en compte pour en diminuer le coût. A noter que la plupart de ces préconisations sont valables pour de la grande série, et ne rentre peut-être pas en ligne de compte sur des petites quantités, la fabrication de PCBs "prototypes" en petite série ne permettant pas de bénéficier d'économies d'échelle.

D'une façon générale, chaque étape de fabrication c'est du temps machine + du temps d'opérateur + de l'usure machine + du consommable. Si vous en supprimez - parce que ce n'est pas strictement nécessaire pour avoir un PCB qui marche, ça coûte moins cher.

Géométrie Difficile de donner des règles générales, mais dans la grande majorité des cas la géométrie des formes dessinées pour les pistes ne fait pas varier le prix. Potentiellement, s'il y a beaucoup de vecteurs (exemple : une image bitmap traduite en GERBER sur le cuivre ou la sérigraphie) cela peut être facturé plus cher. Sur du prototypage je n'ai jamais vu de contraintes à ce sujet. En général c'est plus simple : si les machines n'arrivent pas à faire les typons, ce n'est pas plus cher, par contre le dossier est refusé.

Surface Plus yen a, plus c'est cher. Si vous voulez économiser, routez serré ! Et idéalement cherchez même à faire rentrer plusieurs PCBs dans un rectangle plus grand, qui sera inférieur ou égal à la taille de panneau du fabricant. Si celui-ci n'est pas un chacal (et ne vous les sépare pas de force) ça vous reviendra mécaniquement deux fois moins cher que de faire les cartes une par une. Et dans ce cas : Tetris Master is your friend.

Classe de routage Plus la classe est élevés, plus c'est cher, car il faut réquisitionner les machines les plus performantes de l'usine, et il faut faire plus de contrôles. La classe standard dans le domaine industriel aujourd'hui c'est la classe 4. Au-dessus, très probable - mais pas systématique - qu'il y ait un surcoût. D'une façon générale, pour s'éviter des problèmes, il ne faut pas router au-dela de la classe max requise par le composant limitant (souvent ce sont les BGA avec un pitch ultra-serré qui font chier). Idéalement, si il n'y a que quelques composants qui imposent une classe élevée, ne pas router toute la carte dans cette classe, rester dans une classe plus basse (viser classe 4), et ne router à la classe requise que localement autour du/des composants qui posent problème.